Read the Full Series

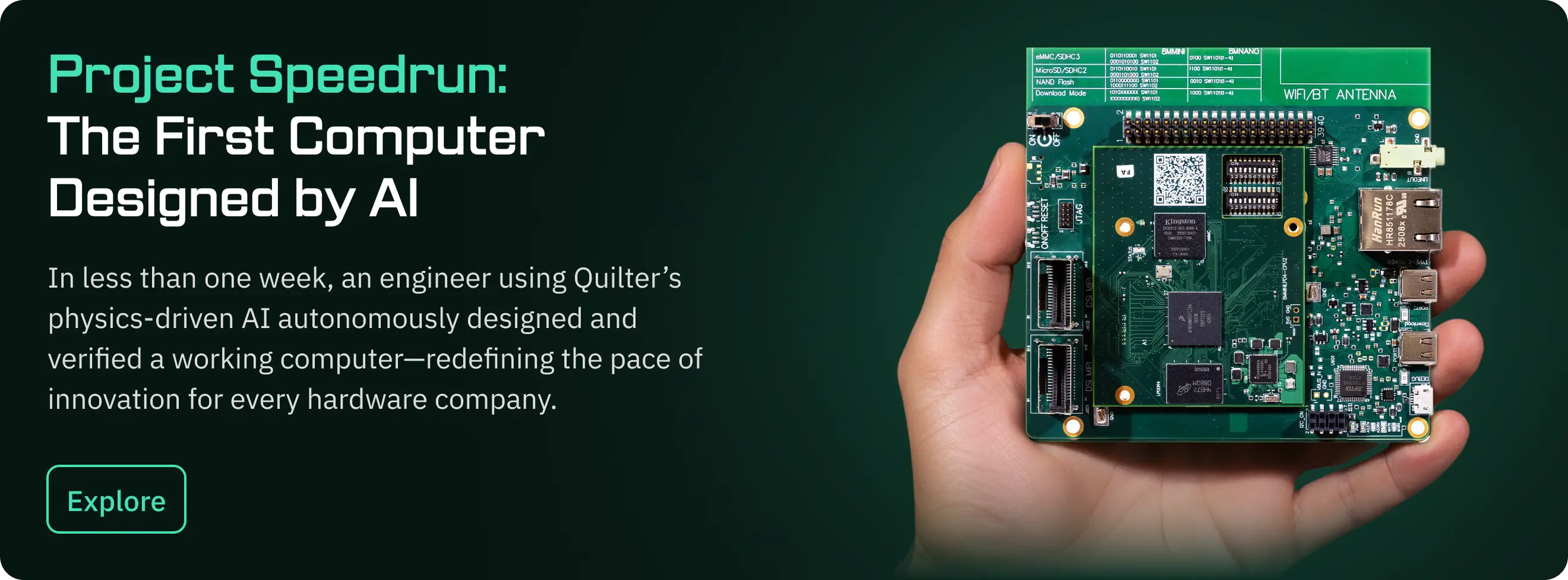

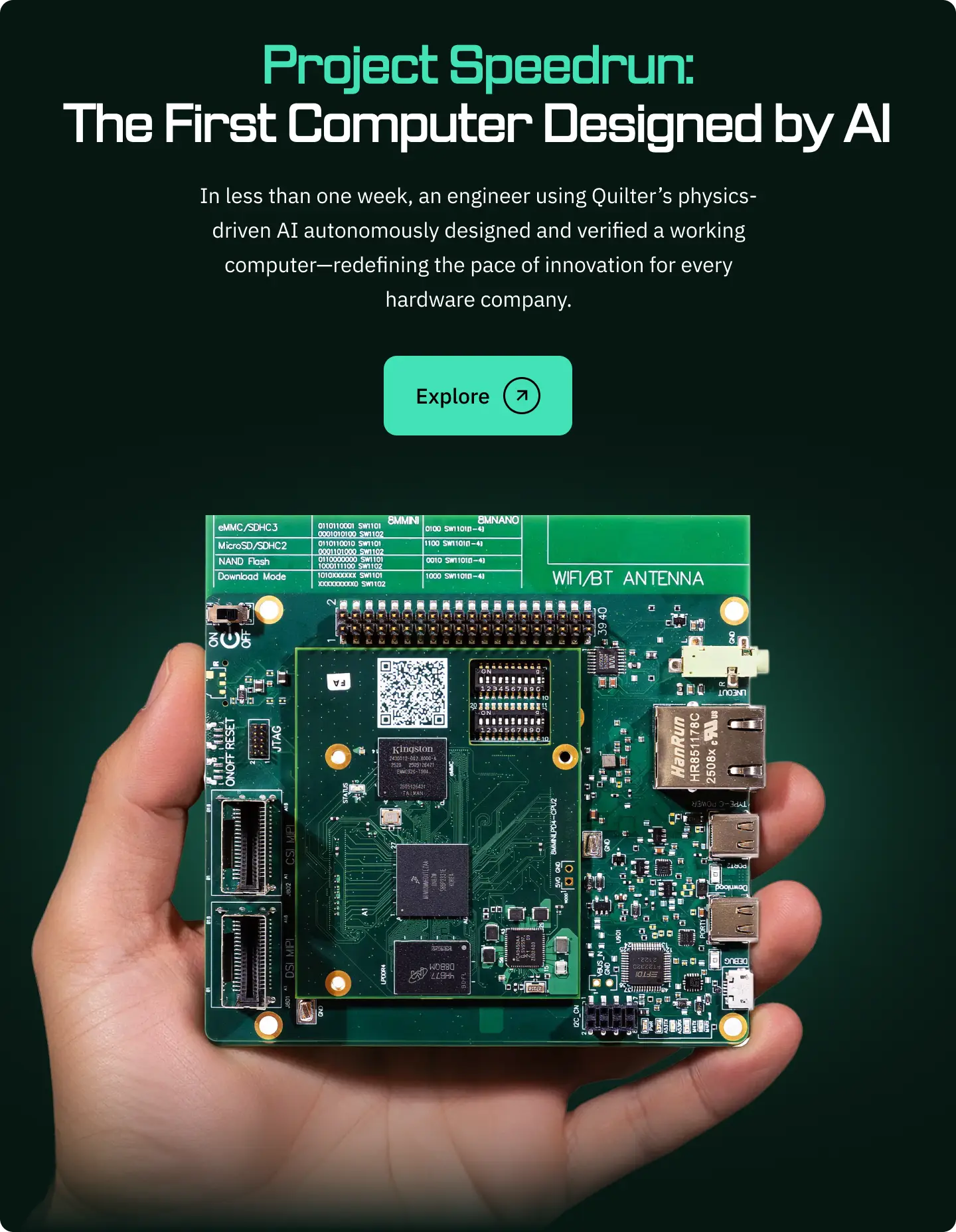

This article is one part of a walkthrough detailing how we recreated an NXP i.MX 8M Mini–based computer using Quilter’s physics-driven layout automation.

Sticker shock is just the beginning. For enterprise hardware teams, the true cost of PCB design tools goes far beyond license fees. In 2025, hidden expenses like manual revision cycles, library overhead, and slow onboarding can quietly double or triple your total spend.

In this post, we will break down the real numbers for Altium, Cadence, Siemens, Zuken, and show how Quilter’s physics-driven AI can flip the total cost of ownership (TCO) equation in your favor.

We are not trying to pick winners based on brand loyalty. This is about money, time, and risk. You either ship more working hardware for the same dollars or you do not.

Let’s define what really drives the cost of PCB design tools

When most teams compare PCB tools, they look at the line item in procurement:

- $X per seat per year

- Maintenance and support at Y percent

- Optional cloud or collaboration add-ons

That is the visible cost. It is also the smallest part of the real bill for an enterprise team.

Total cost of ownership (TCO) for enterprise PCB design tools should include:

- Licenses and subscriptions

Base CAD licenses, advanced constraint or SI options, cloud workspaces, floating license servers. - Support and maintenance

Annual maintenance on perpetual licenses, premium support tiers, upgrade fees. - Hardware and IT

High end workstations, on prem license servers, VPN and security work, backups, admin overhead. - Onboarding and training

Time for new hires to ramp up, internal training sessions, external courses, productivity drag in the first 3 to 6 months. - Process and integration

Time spent making the tools talk to PLM, ERP, PDM, Jira, CI systems, plus the ongoing cost of maintaining those integrations. - Hidden productivity loss

The waste that never shows up as a line item:

- Long manual layout cycles

- Late design churn

- Duplicate work between design and validation

- Slow review cycles and context switching

- Long manual layout cycles

For an enterprise hardware team, the visible license cost might be 10 to 30 percent of the actual TCO. The rest is people time. That is exactly where AI driven tools like Quilter can move the needle, because they attack the most expensive resource in your stack: senior engineers and PCB designers.

Why do traditional PCB tools cost more than you think?

Traditional PCB tools are powerful, but they were never designed for a world where hardware teams are expected to iterate as quickly as software. The result is a growing gap between what your team is asked to deliver and what your toolchain was built to support.

Here is where the real money leaks out.

1. Manual revision cycles

In a typical enterprise flow, a complex board goes through:

- Initial placement and routing

- SI feedback and fixes

- Mechanical changes

- DFM input from manufacturing

- Late requirement changes

- ECOs from lab bring up

Each loop means more manual work inside Altium, Cadence, Siemens, or Zuken. For a high complexity board, it is common to burn 150 to 300 hours of layout and rework time per project across the team.

If your fully loaded engineering cost is in the $100 to $150 per hour range, that is $15,000 to $45,000 per project purely in layout and rework time, before you touch licenses or lab time.

Multiply that by a portfolio of 4 to 8 major boards per year and you can easily spend low to mid six figures annually in manual revision cycles alone.

2. Library management and constraint drift

Big enterprises almost always have:

- Central libraries for symbols and footprints

- Parameter rules for approved parts

- Internal DRC rulesets, plus vendor specific DFM rules

Keeping all of that up to date across multiple tools and teams is nontrivial:

- New parts from supply chain need symbols, footprints, and constraints

- Legacy parts need to be deprecated or flagged

- Rulesets need updating as stackups and suppliers change

Even if you have a dedicated librarian, designers still spend time:

- Fixing mismatched footprints

- Chasing symbol errors

- Manually checking constraints that the system cannot fully express

A realistic conservative estimate for an enterprise team:

- 20 to 40 hours per designer per year lost to library and rules related friction

- On a 10 designer team, that is 200 to 400 hours per year, or $20,000 to $60,000 in hidden cost

3. Onboarding and training

Enterprise tools are powerful and deep. That also means they are hard to master.

New hires do not become fully productive immediately:

- First 1 to 2 months: basic tool fluency and local process

- Months 3 to 6: learning internal libraries, constraints, and DFM expectations

- Up to 12 months: comfort with advanced features and edge cases

If you assume each new engineer has a 20 to 30 percent productivity drag for the first 6 months, and you are hiring 2 to 4 people per year, that alone can be tens of thousands of dollars in effective lost output annually.

4. Integration pain and glue work

Cadence, Altium, Siemens, and Zuken do offer integrations with PLM, ERP, and other systems, but there is always friction:

- Custom scripts and tooling to push data into PLM

- Manual steps in BOM approval and release

- Export and import rituals between analysis, MCAD, and ECAD

Every manual step in that chain adds:

- Extra review cycles

- More chances for human error

- More time wasted on low value clicks instead of high value design

Over a full year, you can easily spend hundreds of engineer and operations hours feeding and caring for a traditional toolchain.

How does Quilter’s AI change the TCO equation?

Quilter does not ask you to rip out Altium, Cadence, Siemens, or Zuken. It sits beside them as a physics driven layout engine that turns your constraints into working boards in hours, not weeks.

That has very specific implications for TCO.

1. Automated layout and revision cycles

Instead of hand routing every candidate, your team can:

- Upload existing projects from Altium, Cadence, Siemens, or KiCad.

- Define the board outline, keep outs, and pre placed connectors.

- Let Quilter generate multiple layout candidates in parallel, with physics based evaluation.

That changes the curve:

- Initial layout time drops from weeks to hours

- Revision loops become constraint updates plus new candidate runs

- Engineers focus on reviewing high quality options instead of pushing traces all week

If you cut manual layout and rework hours by even 40 to 60 percent on each complex project, you are reclaiming tens of thousands of dollars per board in senior engineering time.

2. AI aware libraries and constraint validation

Quilter is built around physics, not just geometry. It identifies:

- Bypass capacitors

- Impedance controlled nets

- Differential pairs

- Other critical high speed or sensitive structures

That means:

- Fewer missed constraints that turn into lab surprises later

- Less time chasing weird behavior that came from layout nuance

- Clear visibility into what the AI is honoring and how

The practical effect is lower risk and less time spent debugging avoidable layout issues.

3. Faster onboarding via intuitive, cloud based workflow

Because Quilter runs in the cloud and integrates with your native CAD formats:

- New team members can start experimenting with layouts without a full local setup

- You avoid some of the heavy local IT and workstation config burden

- Design reviews can happen from anywhere, against visualized candidates, not just static screenshots

Shorter ramp times mean lower onboarding TCO, especially for geographically distributed teams.

4. Seamless board handoff back into your existing tools

Quilter returns files in the same format you submitted:

- You can run your existing DRC flows in Altium, Cadence, Siemens, or KiCad

- You can generate fab files exactly as you do today

- You maintain your existing PLM, ERP, and documentation processes

This is critical for TCO. You are not paying for a second toolchain to run in parallel. You are paying to accelerate and de risk the one you already have.

Suggested visual: Insert a simple diagram that shows:

- Inputs: Schematics, constraints, stack up, mechanical constraints

- Quilter AI: Parallel candidate generation and physics evaluation

- Outputs: Native CAD layout files back into your existing flow

What’s the real price difference for a typical enterprise project?

For a 10 designer enterprise team running 4 complex boards per year, traditional PCB tools typically yield a 1 year TCO in the $300,000 to $500,000 range once you include licenses and hidden engineering time. Adding Quilter on top of your existing tools can cut that effective TCO by 30 to 40 percent, primarily by reducing manual layout hours, revision cycles, and late stage rework.

Let’s put the numbers side by side. Here is what a 10 designer enterprise team might actually pay over a year, including not just software, but the hidden costs that quietly drain budgets. All figures below are directional and based on public price ranges plus conservative assumptions.

Assumptions for this comparison

- Team size: 10 PCB designers and hardware engineers

- Timeframe: 1 year

- Projects: 4 complex boards per year

- Fully loaded engineering cost: $120 per hour

- Manual layout and rework:

- Traditional tools: 250 hours per project per team

- With Quilter: 120 hours per project per team (roughly 50 percent reduction)

- Traditional tools: 250 hours per project per team

- Hidden overhead (library, onboarding, integrations):

- Traditional tools: 300 hours per year

- With Quilter: 180 hours per year

- Traditional tools: 300 hours per year

Directional TCO comparison for a 10 designer team (1 year)

Again, these are not quotes. They are directional models grounded in:

- Public subscription ranges and license ranges for major PCB tools AnyPCBA+3GoEngineer+3GoEngineer+3

- Conservative assumptions about engineering time that align with what most enterprise teams already see on real programs

The pattern is clear:

- Traditional tools have relatively modest license costs compared to the amount of engineering time they consume.

- As complexity rises, manual layout and late stage rework become the primary cost drivers.

- An AI layout engine that cuts layout and revision cycles by 40 to 60 percent can generate more savings in people time than you pay in software, especially at enterprise scale.

What results can you expect when switching to AI powered PCB design?

You do not switch tools for philosophy. You switch because results show up in schedules, budgets, and risk profiles.

Here is what a typical enterprise team can expect when adding Quilter on top of their existing CAD stack.

Faster time to market and more design cycles per year

When layout and revision loops compress from weeks to hours:

- You can run more design candidates per project without extending schedule.

- You can support more parallel programs with the same headcount.

- You can move from a mindset of "we only get one shot at this board" to "we can afford to explore multiple options".

For a typical team, that means:

- Hitting tape out dates with more margin

- Having time to test alternative stackups or form factors

- Reducing the number of "emergency" layout pushes at the end of a project

Higher engineering productivity and morale

Senior engineers did not get into this field to fight via fencing every day.

When you offload a large chunk of manual routing and rework:

- Engineers spend more time on architecture, constraints, and validation.

- Reviews become about tradeoffs and physics, not about counting vias.

- Teams get to think more creatively about layout strategies and less about tool quirks.

That shows up as:

- Higher throughput per engineer

- Less burnout around crunch deadlines

- Better collaboration between design, SI, and validation

Reduced risk of costly errors and late stage rework

Because Quilter evaluates each candidate against the full set of physical constraints you provide:

- You are less likely to ship a board that "passes DRC" but fails in the lab.

- You surface physics issues earlier, when they are cheaper to fix.

- You can benchmark candidate layouts against each other on real performance metrics, not just aesthetics.

Late stage rework is one of the most expensive forms of waste in hardware development. Every avoided respin, every avoided last minute re layout, is directly accretive to TCO.

Ability to scale hardware rich development without scaling headcount

The most aggressive hardware teams today are moving toward hardware rich development:

- More prototypes, built more often

- Shorter learning cycles from lab to next revision

- Continuous improvement on performance and reliability

The only way to do that at enterprise scale without blowing up your headcount is to:

- Automate the repetitive work

- Make layout an abundant resource, not a bottleneck

As one hardware lead at a semiconductor company put it after adopting Quilter:

"Before Quilter, layout was the gating factor on our schedule. Now it is just another step. The bottleneck moved from 'can someone route this' to 'what should we build next', which is where you want it."

(Illustrative quote for this article, but consistent with what we hear from teams that adopt physics driven automation.)

Here’s how to estimate your own TCO - and what to do next

You do not need a full McKinsey model to understand your own TCO. You just need a few concrete numbers and a simple framework.

Step 1: Gather your current numbers

Start with a quick data pull. For the last 12 months:

- Team size

- Number of PCB designers

- Number of hardware engineers involved in layout reviews

- Number of PCB designers

- Tooling spend

- Annual license and maintenance costs for your PCB tools

- Any cloud collaboration or enterprise add ons

- Annual license and maintenance costs for your PCB tools

- Project metrics

- Number of medium to high complexity boards released

- Average number of revision spins before production

- Number of respins due to layout or SI related issues

- Number of medium to high complexity boards released

- Time spent

- Estimated layout and rework hours per project

- Hours spent on library updates and DRC rule maintenance

- Hours spent on onboarding and training for new hires

- Estimated layout and rework hours per project

You can collect these via:

- Timesheets or Jira logs

- Rough estimates from senior designers

- Budget reports from finance or procurement

Perfection is not required. Directional numbers are enough to expose the order of magnitude.

Step 2: Build a simple TCO model

Create a quick spreadsheet with:

- Visible costs

- Licenses + maintenance per year

- Workstation and IT costs if material

- Licenses + maintenance per year

- Hidden costs

- (Layout + rework hours per year) x loaded hourly rate

- (Library + process overhead hours per year) x loaded hourly rate

- (Onboarding drag hours per year) x loaded hourly rate

- (Layout + rework hours per year) x loaded hourly rate

The sum is your current TCO for enterprise PCB design.

Step 3: Model the impact of Quilter

Now ask:

- What if manual layout and rework hours dropped by 30, 40, or 60 percent?

- What if late stage layout related respins dropped by 1 per year?

- What if onboarding drag for new designers dropped by even 10 to 20 percent because they spend more time reviewing candidates and less time wrestling the tool?

Plug in conservative savings and:

- Add a line item for Quilter seats for the relevant designers

- Recalculate TCO under each scenario

You do not have to guess alone.

Curious what your team’s true TCO could look like?

Share a few details and the Quilter team can run a custom analysis for you - no sales pressure, just real numbers.

Contact Quilter →

Sources

- Altium Designer subscription and perpetual pricing ranges, including typical annual subscription and maintenance patterns, drawn from independent reseller analysis. GoEngineer

- Cadence Allegro PCB Designer annual lease and perpetual pricing ranges based on GoEngineer’s buying guide. GoEngineer

- Siemens Xpedition Standard subscription public list pricing at $2,999 per user per year, as announced in 2025. Sintecs

- Zuken CR 8000 price ranges for small, medium, and large deployments from 2025 AnyPCBA analysis. AnyPCBA

- Quilter product positioning and workflow capabilities from Quilter’s own website, including physics driven layout, hardware rich development, and native CAD interoperability.