設計を数時間で完了

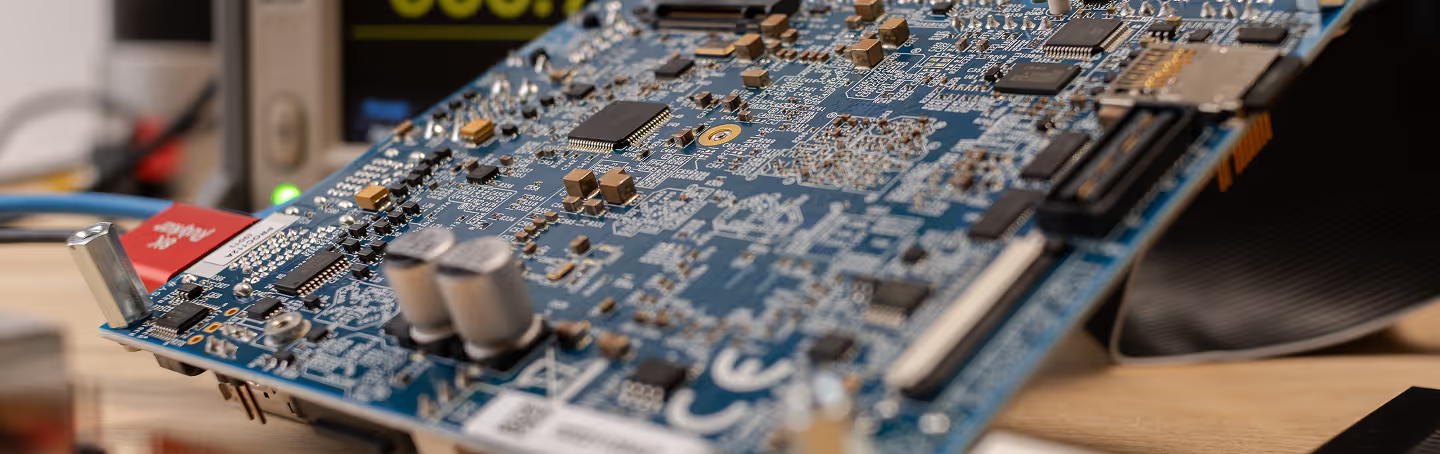

基板レイアウトは、あらゆるハードウェア開発のボトルネックになりがちです。Quilter は、配置配線と物理検証まで、レイアウト全体を自律的に完了できる初の仕組みです。差動配線、DDRタイミング、クリアランスなどを生成中に適用します。基板設計者は製品を決める複雑な基板に集中でき、エンジニアはシステム統合に集中できます。最速で学ぶチームが勝ちます。設計サイクルごとに10倍の選択肢を生み出すほど、学びを加速するものはありません。

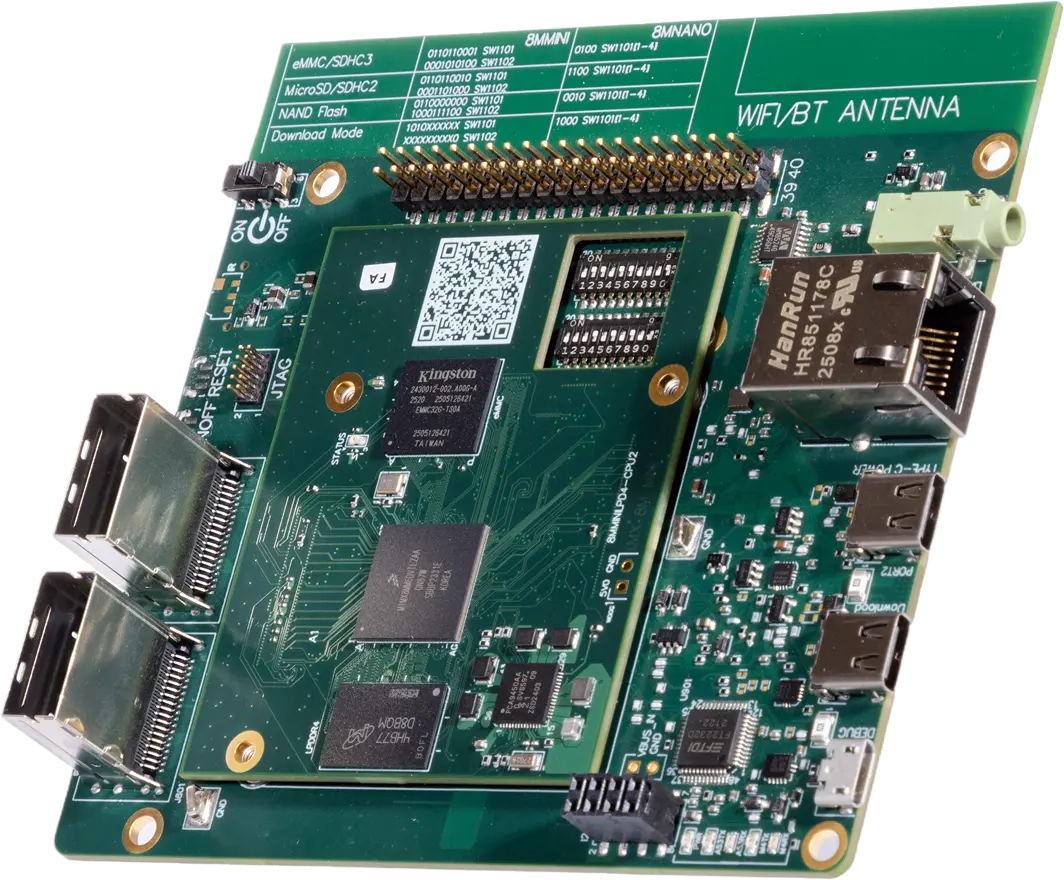

数時間で複数の候補を生成。すべての配線トレースを物理で検証

%202.avif)

基板レイアウトは、あらゆるハードウェア開発のボトルネックになりがちです。Quilter は、配置配線と物理検証まで、レイアウト全体を自律的に完了できる初の仕組みです。差動配線、DDRタイミング、クリアランスなどを生成中に適用します。基板設計者は製品を決める複雑な基板に集中でき、エンジニアはシステム統合に集中できます。最速で学ぶチームが勝ちます。設計サイクルごとに10倍の選択肢を生み出すほど、学びを加速するものはありません。

.svg)

Quilter は『不可能』だと学習していないからこそ、『不可能』な解を見つけます。LLMが模倣し、オートルータが迷路解きする一方で、強化学習は設計空間を能動的に探索します。各エージェントは部品を配置配線し、物理を評価し、より良い結果につながる選択を学びます。数百万回の反復が配置配線戦略を洗練し、人のバイアスなしに制約を両立させ、『使える』非定型な配線手法や配置戦略を生み出します。

現状維持派が「AIの過剰宣伝」と呼ぶものを、私たちは「最適解」と呼びます。

アーサー・C・クラーク

ハードウェアは、アイデアを試し、バリエーションを作り、速く学ぶことで前に進みます。Quilter はボトルネックを取り除き、より多くの基板を出荷し、より多くの実験を走らせ、より速く学べるようにします。

ゼロから始める。前回の正解ではなく、この設計で『使える』ものを見つける。

回路図と制約条件をアップロード。重要ネットは保持しつつ、過去の妥協は引き継ぎません。

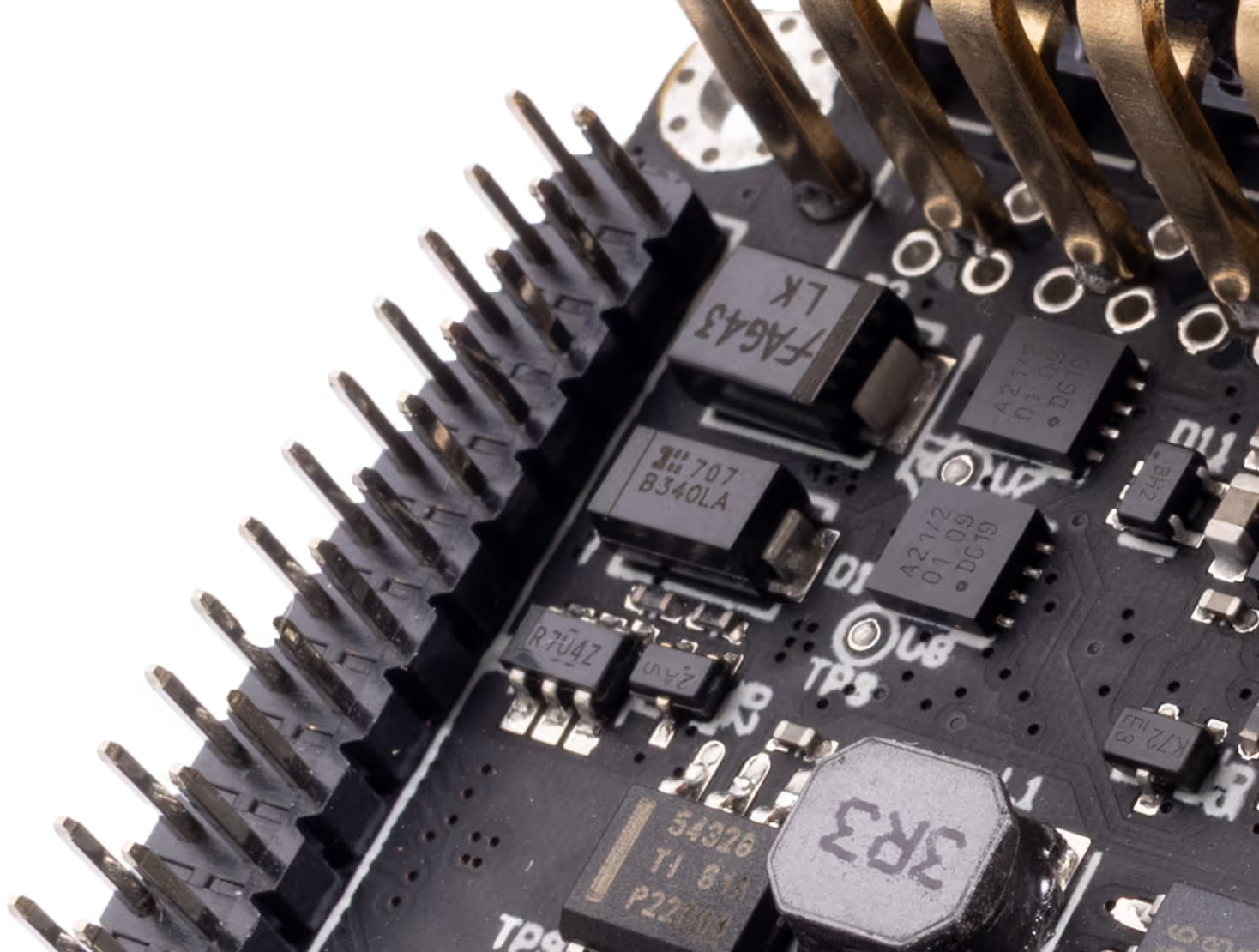

数百の候補を並列に生成。各候補は物理制約で検証された“発見”になり得ます。

実際の配置配線済みレイアウトを比較。仮定ではなく測定結果に基づいて選び、エクスポートしてテストします。

アイデアから検証済みハードウェアまでの距離が、競争力を決めます。工数を取り戻し、イノベーションを速め、遅延を減らすことで、学びを加速します。

月曜にテスト基板を出し、金曜には学びを得る。順番に進めれば数か月かかる実験も、並列で走らせられます。ハードウェアがない1週間は、競合がより多く学ぶ1週間です。

企業のイノベーション目標は、ソフトウェアのような反復を前提にしています。Quilter は、その前提を現実にします。同じ期間で10倍のコンセプトを検証し、『新製品導入(NPI)』の目標達成を後押しします。

悪いアイデアは数日で消え、数か月はかかりません。良いアイデアはすぐに次へ進めます。実験コストが数週間ではなく数時間なら、常識外れな案も試せます。

アイデアのキューは実験ポートフォリオになります。市場タイミングの仮説を、意味があるうちに検証できます。機会の窓が閉じた後ではなく、その中でイノベーションを届けます。

最高の基板設計者は、最も難しい問題に集中できます。定型基板が複雑な基板の後ろで待つことはありません。すべての設計に、疲れた妥協ではなく、物理に基づく新しい探索を。

反復が10倍なら、学びも10倍。差はサイクルごとに広がります。競合が議論している間に、あなたはすでに試し、学び、前に進んでいます。