Solutions

By Design Type

By Industry

Hardware-Rich Development

.webp)

Quilter を使ったエンジニアは、2枚構成(SOM+ベースボード)を完成させました。ベースボードのクリーンアップは12時間(手作業レイアウト見積:238時間)、SOMのクリーンアップは26.5時間(同:190時間)。合計で、人の作業38.5時間が、推定428時間の手作業を置き換えました。

ハードウェアチームは、四半期単位のレイアウトサイクルから週次の学習ループへ移行できます。各設計が、検証し、試し、競合より速く前進するための機会になります。

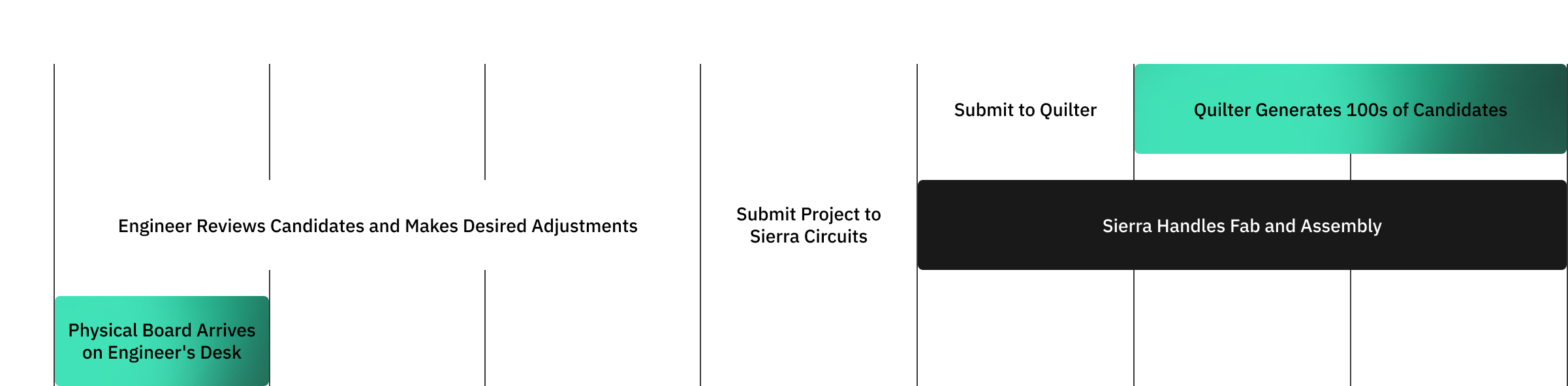

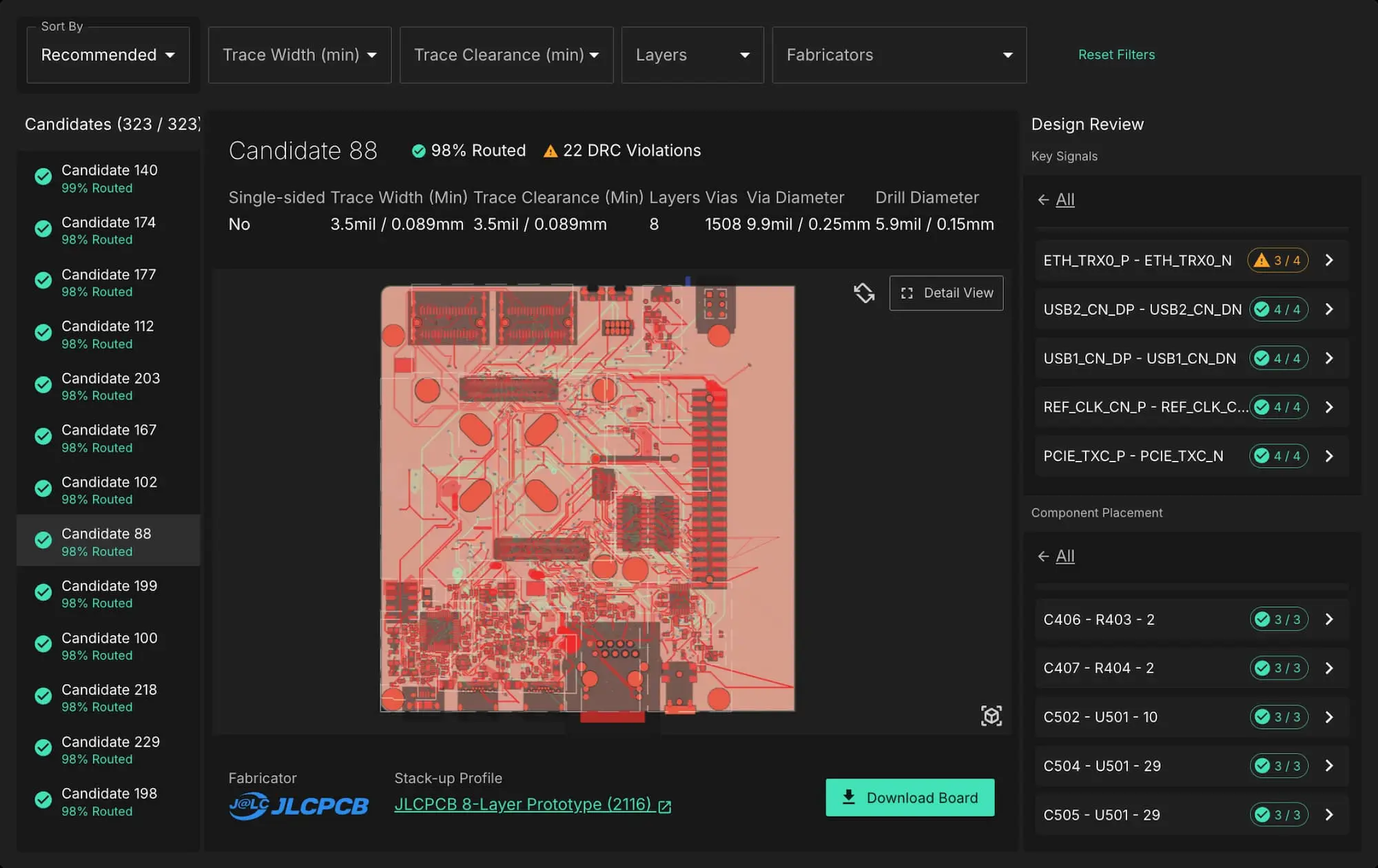

SOM+ベースボードの設計は、NXP i.MX 8M Mini の評価プラットフォームをベースにしました。スタッフ・エレクトリカルエンジニアの Ben Jordan が、設計と制約条件を整えてジョブを投入。Quilter は同じ制約条件のもとで複数のジョブを並列に実行し、27時間でレイアウトを完了。さまざまな候補を評価して順位付けし、複数の有力案として返しました。

Quilter が反復的な作業を担い、エンジニアは主導権を維持しました。配置配線と物理チェックをQuilterが担うことで、Ben はファームウェア準備、ドキュメント整備、制約条件の調整に工数を振り向けられました。サプライチェーンの小さな問題(コネクタの欠品、Wi‑Fiモジュールの採用取り止め)も即時に解決し、反復に遅れはありません。クリーンアップは最小限で、PDN(電源配電網)のベタ、ビアのクラスタ、軽微なフットプリント差し替えのみ。配線の引き剥がしもリスピンもありませんでした。

Project Speedrun は、Quilter の物理法則に基づくAIが、構想段階から実用段階へ到達したことを示します。

コアアーキテクチャ

結果

Quilter使用時の人の設計時間

38.5時間

• SOM: 12時間

• ベースボード: 26.5時間

Quilter使わない人の設計時間

428時間

• SOM: 190時間

• ベースボード: 238時間

Quilter実行時間

27時間(配置配線+物理検証)

配線完了率

98%

立ち上げ

両基板とも初回電源投入で成功—リスピンなし

本プロジェクトは、自動車のインフォテインメント、安全装置、マシンビジョン用途で一般的な複雑な組込みコンピューティングハードウェアを、Quilter が自律的に完成させられることを示します。

コアアーキテクチャ

プロセッサ

NXP i.MX 8M Mini Quad (4 × Cortex-A53 @ 1.8 GHz)

メモリ

2 GB LPDDR4 (32-bit bus width)

ストレージ

32 GB eMMC 5.1 (upgraded from 16 GB reference part)

フラッシュメモリ

32 MB QSPI NOR Flash

オーディオ

24-bit / 192 kHz DAC, 3.5 mm headphone jack

ネットワーク

10 / 100 / 1000 Mbps Ethernet

拡張

M.2 connector supporting PCIe

基板設計

フォームファクタ

2枚構成:System-on-Module(SOM)+ベースボード

PCB積層構成(スタックアップ)

Sierra Circuits製造の8層HDI構成

配線幅/配線間隔

2 mil(SOM)/3.5 mil(ベースボード)

部品点数

合計843

ピン数

合計5,141

配置配線

Quilter AIが完全自動化

詳細なストーリーと技術的な洞察を通じて、仕組みと重要性を全体像として把握できます。

製造と実装は Sierra Circuits と協力しました。ベースボードは標準の「製造3日+実装3日」スケジュールで完了。一方、SOM の2 mil HDIジオメトリは、Sierra の高度HDI精度・短納期プロセスラインを使うため、より長いリードタイムが必要でした。料金は標準の商用レートで、誰でも利用できる通常の発注手順を使用し、特別扱いは受けていません。つまり、汎用のサービスを使って誰でも同様の結果を再現できます。

Quilter が物理法則に基づくレイアウトを生成する前に、設計の準備が必要です。制約条件を定義し、意図を表現し、構造を明確化します。この準備ステップの詳細は、最初のブログ記事をご覧ください。