Solutions

By Design Type

By Industry

Hardware-Rich Development

.webp)

Ein Ingenieur, der Quilter nutzte, fertigte das Zwei-Platinen-System mit 12 Stunden Nacharbeit am Baseboard statt der 238 Stunden, die für ein manuelles Layout veranschlagt waren, sowie mit 26,5 Stunden Nacharbeit am System-on-Module (SOM) statt der 190 Stunden für dessen manuelles Layout. Insgesamt ersetzten 38,5 Stunden menschliche Arbeit 428 Stunden geschätzten manuellen Aufwand.

Hardware-Teams können nun von quartalsweisen Layoutzyklen zu wöchentlichen Lernschleifen wechseln und jedes Design in eine Chance verwandeln, zu testen, zu iterieren und der Konkurrenz voraus zu sein.

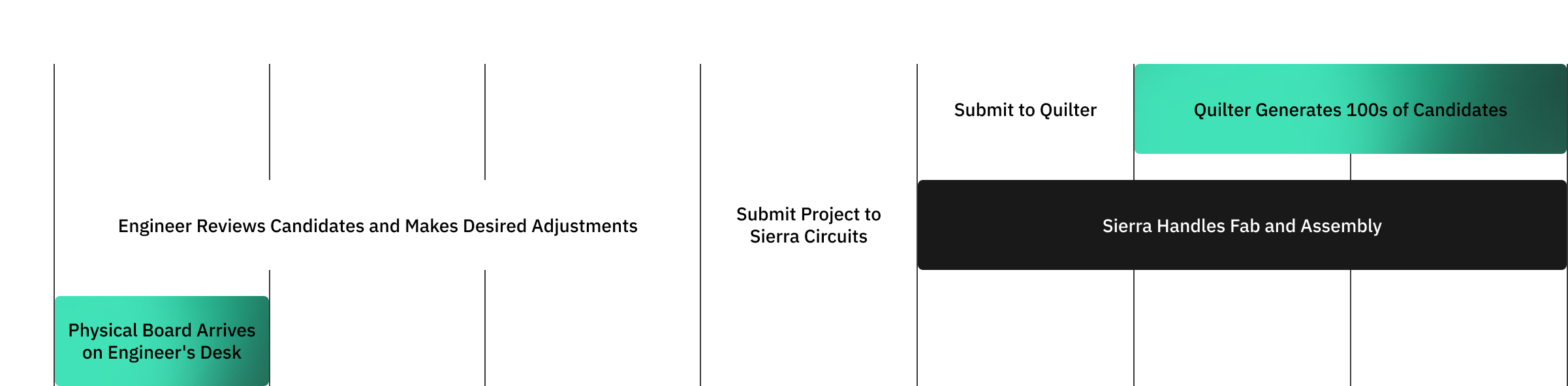

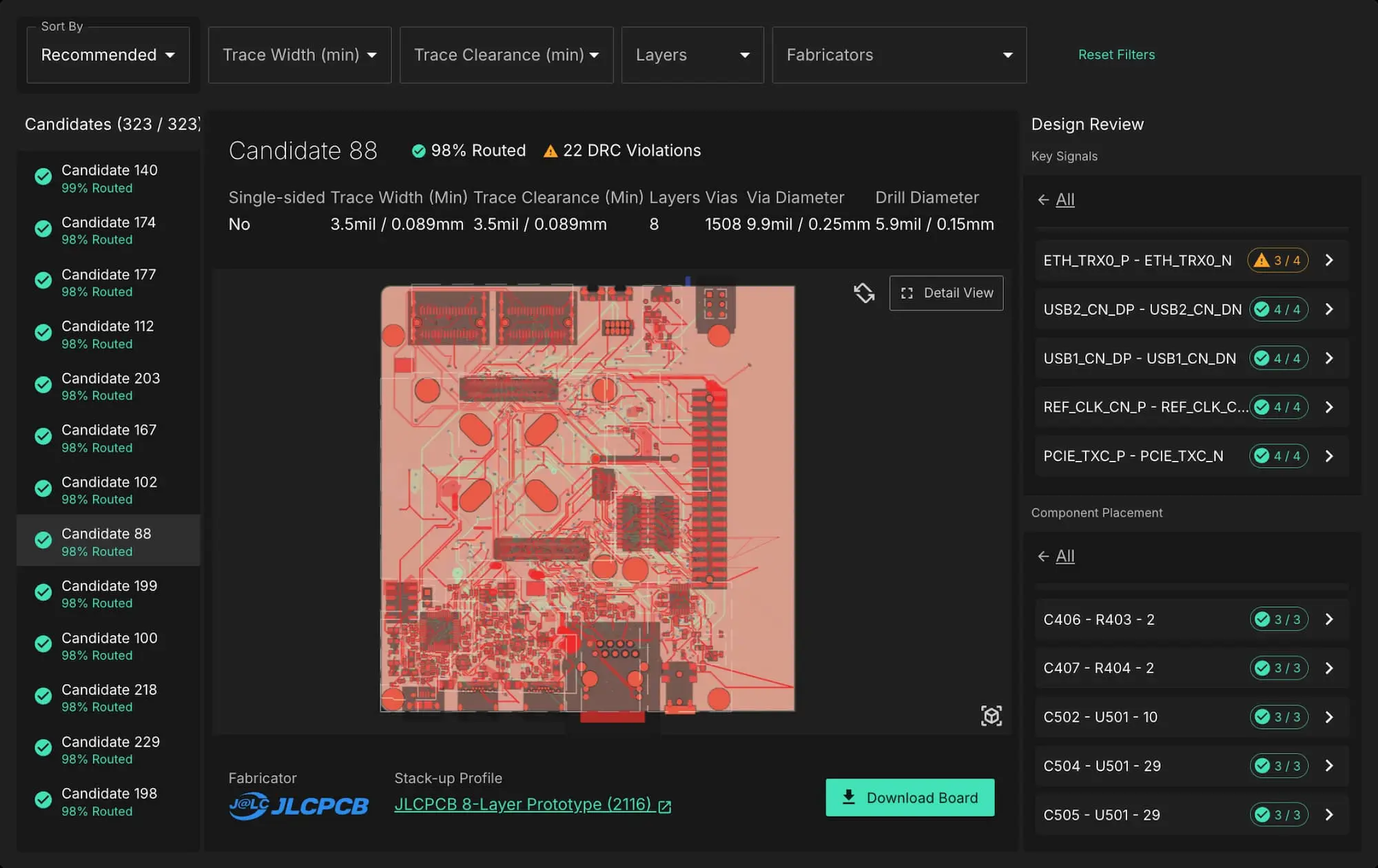

Wir haben uns dafür entschieden, unser System-on-Module- (SOM) + Baseboard-Design auf die NXP-i.MX-8M-Mini-Evaluationsplattform zu stützen. Staff Electrical Engineer Ben Jordan hat das Design und die Constraints für die Platinen vorbereitet und die Jobs eingereicht. Quilter führte parallele Seeded-Runs mit unterschiedlichen Constraints aus, schloss das Layout in 27 Stunden ab und lieferte mehrere bewertete Kandidaten.

Quilter übernahm die repetitive Designarbeit, während der Ingenieur die Kontrolle behielt. Die Automatisierung erledigte Platzierung, Routing und Physik-Prüfungen, sodass er sich auf Firmware-Vorbereitung, Dokumentation und Constraint-Verfeinerung konzentrieren konnte. Übliche Lieferketten-Probleme – ein paar nicht lagernde Steckverbinder und ein weggefallenes WLAN-Modul – wurden sofort ohne Iterationsverzögerung gelöst. Die Nacharbeit war minimal: PDN-Flächen, Via-Cluster und kleinere Footprint-Tausche – keine Rückbauten, keine Re-Spins.

Project Speedrun belegt, dass Quilters physikgesteuerte KI von der Idee zur Leistung gereift ist.

Kernarchitektur

Ergebnisse

Menschliche Designstunden mit Quilter

38,5 Stunden

• SOM: 12 Stunden

• Baseboard: 26,5 Stunden

Menschliche Designstunden ohne Quilter

428 Stunden

• SOM: 190 Stunden

• Baseboard: 238 Stunden

Quilter-Laufzeit

27 Stunden (Platzierung + Routing + Physikvalidierung)

Routing-Fertigstellung

98 %

Bring-Up-Ergebnis

Erfolgreicher Erststart auf beiden Platinen – keine Re-Spins

Dieses Projekt zeigt Quilters Fähigkeit, die komplexe Embedded-Computing-Hardware autonom fertigzustellen, wie sie häufig in Automotive-Infotainment, Sicherheits- und Machine-Vision-Systemen verwendet wird.

Kernarchitektur

Prozessor

NXP i.MX 8M Mini Quad (4 × Cortex-A53 @ 1,8 GHz)

Arbeitsspeicher

2 GB LPDDR4 (32-Bit-Busbreite)

Speicher

32 GB eMMC 5.1 (Upgrade vom 16-GB-Referenzbauteil)

Flash-Speicher

32 MB QSPI-NOR-Flash

Audio

24-Bit / 192 kHz DAC, 3,5-mm-Kopfhörerbuchse

Netzwerk

10 / 100 / 1000 Mbit/s Ethernet

Erweiterung

M.2-Anschluss mit PCIe-Unterstützung

Platinendesign

Formfaktor

Zwei-Platinen-System: System-on-Module (SOM) + Baseboard

PCB-Lagenaufbau

8-Lagen-HDI-Architektur, gefertigt von Sierra Circuits

Trace-/Abstandsgeometrie

2 mil (SOM) / 3,5 mil (Baseboard)

Bauteilanzahl

843 insgesamt

Pin-Anzahl

5.141 insgesamt

Platzierung & Routing

Vollständig automatisiert durch Quilter AI

Erhalten Sie durch detaillierte Geschichten und technische Einblicke ein vollständiges Bild davon, wie es funktioniert und warum es wichtig ist.

Für Fertigung und Montage haben wir mit Sierra Circuits zusammengearbeitet. Das Baseboard wurde in einem standardmäßigen 3-Tage-Fab-+-3-Tage-Montageplan fertiggestellt, während die 2-mil-HDI-Geometrie des SOM eine längere Lieferzeit über Sierras Prozesslinie für fortgeschrittene HDI-Präzision und schnelle Durchlaufzeiten erforderte. Wir haben die üblichen kommerziellen Preise gezahlt, denselben Bestellprozess genutzt, der jedem Kunden zur Verfügung steht, und keine Sonderbehandlung erhalten – das beweist, dass jeder diese Ergebnisse mit Standardleistungen reproduzieren kann.

Bevor Quilter ein physikgesteuertes Layout erzeugen kann, muss das Design vorbereitet sein: Constraints definiert, Intention ausgedrückt und Struktur explizit gemacht. Im ersten Blogbeitrag finden Sie eine ausführliche Anleitung zu diesem Vorbereitungsschritt.