インピーダンスプロファイルの自動計算

Quilterは、基板のすべての層における差動ペアとシングルエンドのインピーダンス制御信号について、スタックアップの材料に基づきインピーダンスプロファイルを計算できるようになりました。任意の基板の任意のスタックアップをQuilterに渡せば、目標インピーダンスを達成するために必要なトレース幅とクリアランスでルーティングします。

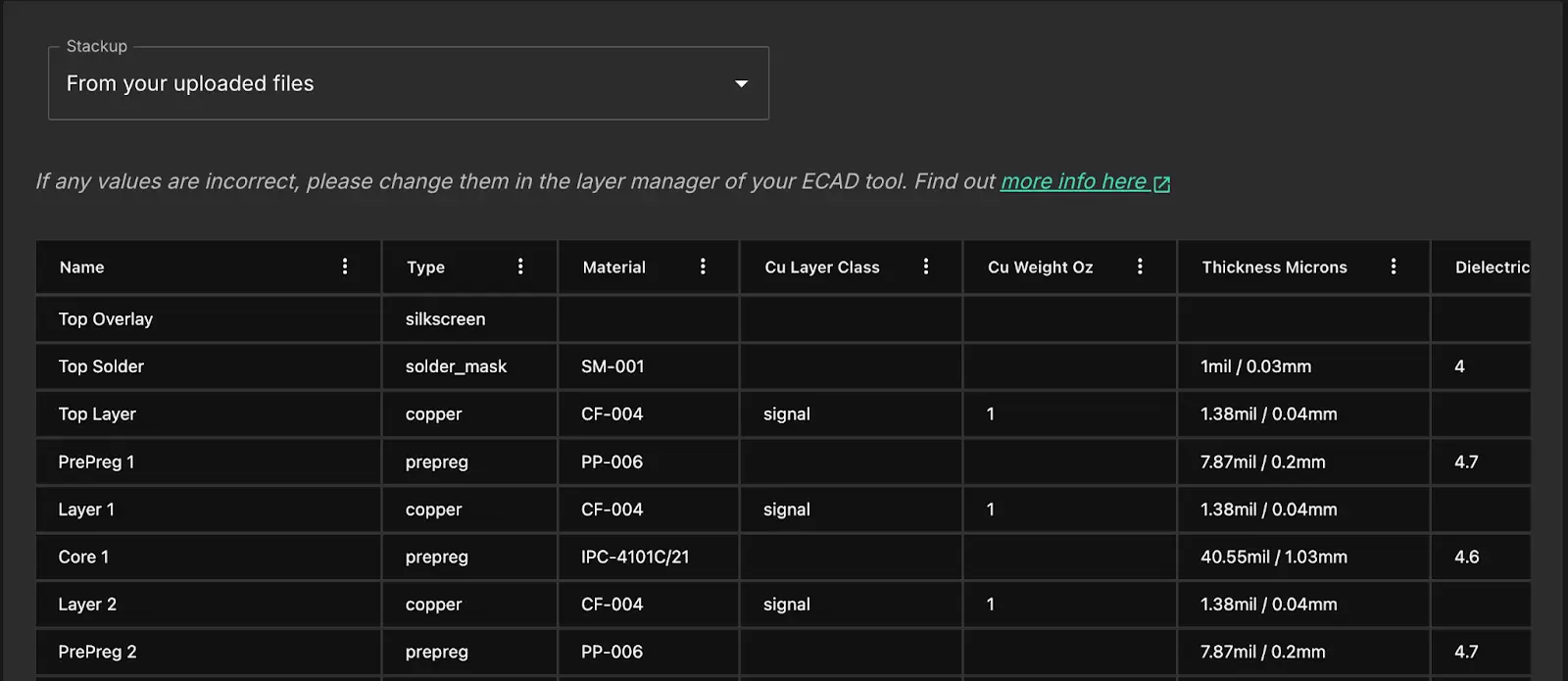

計算には、業界標準のソルバーであるSimberian社のSimbeorを使用しています。Altiumでインピーダンス計算を利用したことがある方は、すでにこのソルバーを使用しています。スタックアップの材料特性が正しければ、インピーダンスプロファイルも正しく計算されます。

プロジェクト:設計による体系的なイテレーション

ジョブはプロジェクトに属するようになりました。プロジェクトは、一つの設計におけるすべてのイテレーション(異なる基板アウトライン、スタックアップ、フロアプラン)を一つの場所にまとめ、進捗を追跡し、残したところから作業を再開できます。

使い方:ホーム画面から新しいプロジェクトを作成し、最初のジョブをアップロードします。そこから、各アップロードが元のBOMの10%以内に収まっている限り、必要なだけジョブを追加できます。10%を超える変更は、新しいプロジェクトを開始します。

重要な理由:ほとんどのQuilterユーザーは、製造に進む前に設計を2〜4回イテレーションします。プロジェクトはこのワークフローを明示的にします:一つの設計、無制限のイテレーション、すべてを一つの場所に。この構造は、同じプロジェクト内の後続イテレーションにおけるソルブ時間の高速化の基盤も構築します。

以前に提出されたジョブは、引き続きジョブ一覧からアクセスできます。今後、すべての新規ジョブにプロジェクトが必要となります。

セットアップの詳細についてはプロジェクトドキュメントをご覧ください。

クリアランス制約、BGAファンアウト

これらの機能は、Quilterが処理できる範囲を大幅に拡張します。それぞれ現在開発中で、段階的にリリースされます。

アップロードされたファイルからの制約

クリアランス制約プロジェクトでは、ECADツールの制約マネージャーに設定できるほぼすべての項目を読み取り、それを遵守します:ビアとネット間、特定ネット間、層ごとのクリアランスを、意図した詳細レベルでサポートします。これは、より強力なDRCチェックと高精度な出力の基盤となります。

BGAファンアウトの自動化

BGAのファンアウト自動生成は、この春にリリース予定です。Quilterは、高密度コネクタを含む多くのフォームファクタでファンアウトとブレイクアウトの両方を生成します。これにより、これまで提出前に手動でファンアウトが必要だった高密度部品をQuilterで処理できるようになります。

.webp)