Read the Full Series

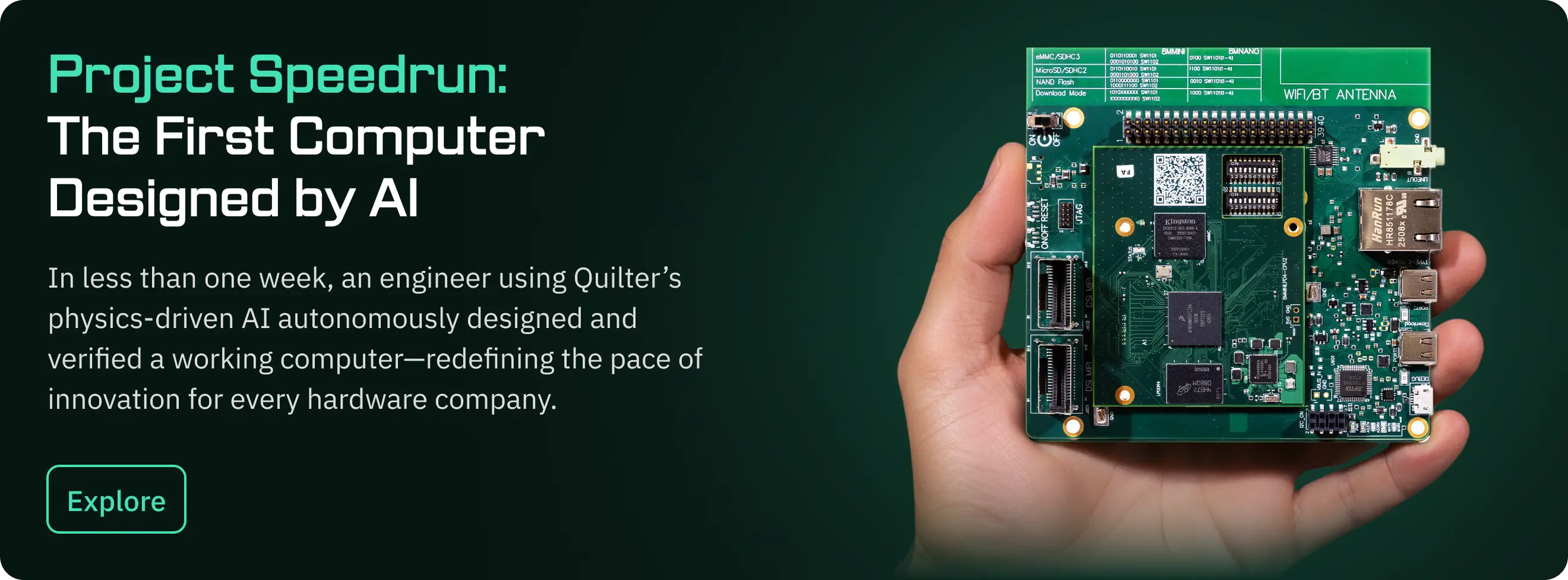

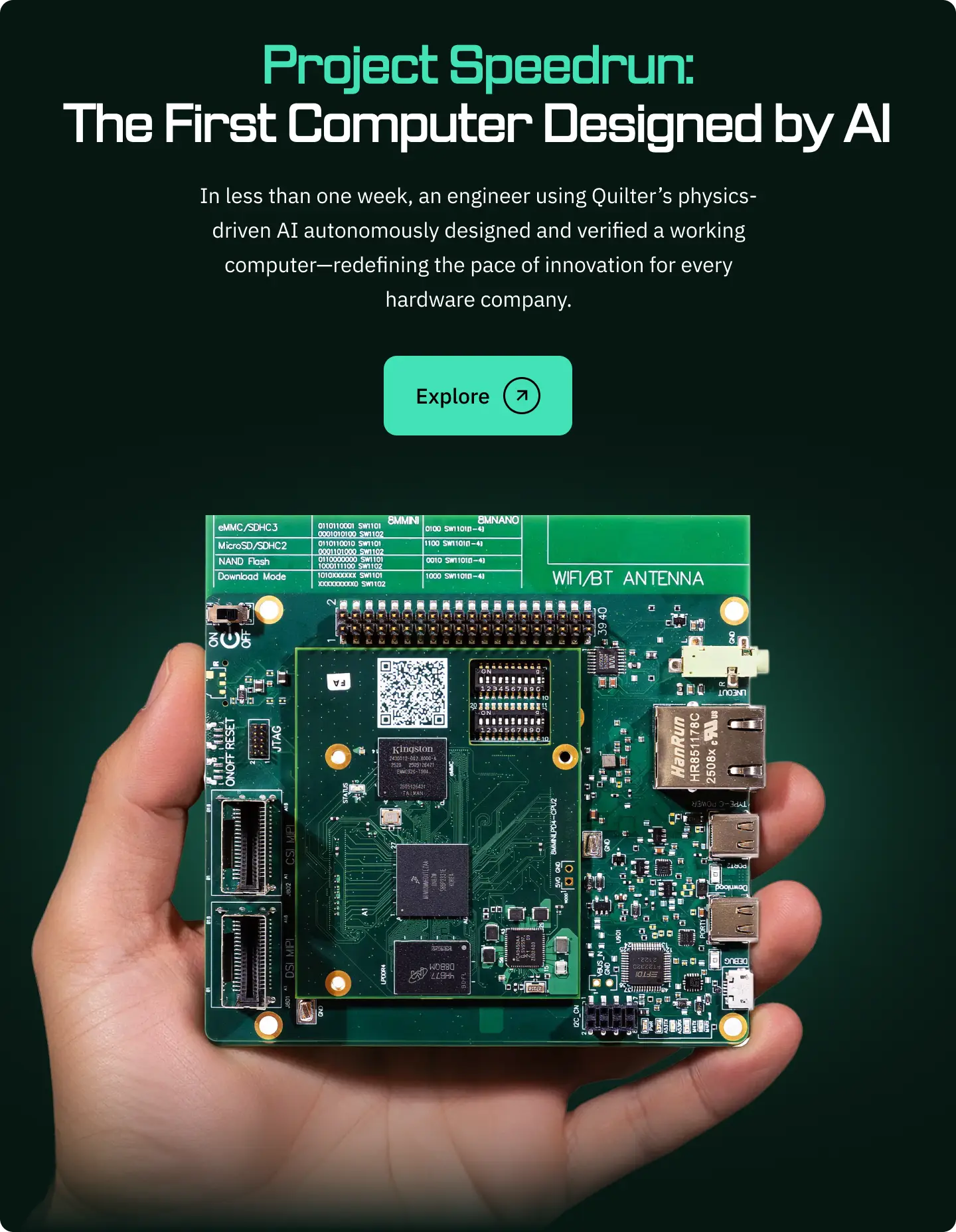

This article is one part of a walkthrough detailing how we recreated an NXP i.MX 8M Mini–based computer using Quilter’s physics-driven layout automation.

If you’ve ever spent hours untangling autorouter results or wondered if PCB layout could finally keep pace with your design cycles, you’re not alone. In 2026, the landscape has shifted: AI-driven tools like Quilter are changing what’s possible for engineers, from startups to aerospace teams. Here’s what you need to know before you choose your next automated PCB routing solution.

This guide is built for engineers and technical decision-makers evaluating automated PCB routing, AI PCB layout, and PCB design automation. You’ll learn how modern autorouters work, how to match tools to your board class and budget, and what results you can realistically expect when comparing Quilter vs Altium, Cadence, and KiCad-style workflows.

What’s Changed in PCB Routing Since 2024?

The biggest change since 2024 is that “automated routing” is no longer a single feature inside your ECAD tool. It’s becoming a distinct workflow: generate candidates, validate them against physics and manufacturing constraints, then choose the best option for final polish.

Traditional autorouters are still rule-driven at their core. You define constraints, set routing rules, and the router tries to connect nets within those rules. On simpler boards this can be helpful. On dense, high-speed, or mixed-signal boards, the classic failure mode hasn’t changed much: you get partial completion, too many vias, awkward detours, and a long tail of manual cleanup.

AI-powered routing flips the goal from “route this board once” to “explore the design space quickly and safely.” Quilter, for example, uses physics-driven AI and reinforcement learning to generate multiple candidate layouts in parallel, then evaluates candidates against constraints so you can pick the best outcome earlier in the cycle. That approach is showing real, measurable time savings in benchmarks: Quilter reported large reductions in routing time and manual post-route adjustments versus Altium Designer and KiCad across multiple board classes.

The practical implication for teams in 2026 is simple: if layout is your bottleneck, the fastest path is rarely “a better autorouter button.” It’s a workflow that reduces iteration cost, increases completion confidence, and gives engineers back engineering bandwidth.

How Do Today’s Leading Autorouters Actually Work?

Most “autorouters” fall into three categories: traditional batch routing, guided interactive routing, and AI-driven candidate generation. They all aim to connect nets, but the way they search for solutions is fundamentally different.

1) Traditional batch autorouting: rule engines plus search heuristics

Classic routers use rules and iterative optimization to find routes. Cadence’s Allegro PCB Router lineage (SPECCTRA) is a well-known example of a shape-based router that focuses on connecting signals and resolving conflicts through its routing process. Cadence has described an approach where the router starts by connecting signals and then resolves constraint conflicts, which is one reason high-end routers can feel more “determined” than entry-level ones.

Strength: strong at enforcing explicit rules at scale.

Tradeoff: the router does not understand intent. It only knows what you told it, and it will happily produce technically legal but practically painful layouts.

2) Guided interactive routing: push-and-shove, glossing, and assisted routing

Modern ECAD tools are excellent at interactive routing: you sketch a path, the router pushes obstacles, respects clearances, and lets you quickly tune. Altium’s ActiveRoute is a good example of “automation that is not a full autorouter.” Altium explicitly describes ActiveRoute as a guided interactive router rather than a complete autorouter, and notes it cannot place vias or handle power routing strategies in the way a full autorouter would.

Analogy: GPS navigation. You are the driver. The tool keeps you from making illegal turns and helps you find a clean path.

3) AI-driven routing and layout: candidate generation plus physics validation

AI-driven PCB layout tries to automate not only the connection step, but also the reasoning around constraints, manufacturability, and physics checks. The easiest way to think about it is “self-driving” rather than “GPS.” You still set the destination (constraints, priorities, keepouts, impedance targets), but the system generates complete candidates and explains what it did.

Quilter’s approach is explicitly built around parallel candidate generation and physics-aware validation. In Quilter’s published benchmarks, the workflow is described as: ingest native project, validate constraints and intent, generate multiple candidates in parallel, run automated physics checks, select the best candidate for final review, then export back to the same native CAD format.

That is not just faster routing. It’s a different way of working: you can evaluate several viable layouts quickly instead of betting your schedule on one long manual route.

Which Solution Fits Your Budget and Board Complexity?

The right “best autorouter software” choice depends on two things that matter more than brand names:

- Board class: simple vs moderate vs dense/high-speed

- Tolerance for manual cleanup: a little polish vs days of rework

Below is a quick self-check that maps common scenarios to tool categories. If you want a single takeaway: traditional tools can be great when you have time and expert operators. AI PCB layout is most valuable when iteration speed and completion confidence are the limiting factors.

A short routing-fit checklist

- Do you route high-speed constraints like DDR, PCIe, USB, HDMI, or sensitive RF paths?

- Do you routinely spend a full day (or more) cleaning up routing after “automation”?

- Do you need to explore multiple stack-ups, form factors, or placement options quickly?

- Do you want automation that still fits into Altium, Cadence, Siemens, or KiCad workflows?

If you answered “yes” to any of the above, you are exactly in the zone where AI-powered PCB design automation tends to pay off fastest.

Budget tiers in 2026 (practical, not theoretical)

Tier A: Free or near-free (best for learning and simple boards)

- KiCad plus external autorouting via FreeRouting is a common route for budget-conscious teams. FreeRouting describes itself as an advanced autorouter compatible with ECAD tools that support Specctra/Electra DSN interfaces, which is why it’s often used as a companion to KiCad workflows.

Best fit: 2-layer to 4-layer boards where interactive routing is acceptable and time-to-cleanup is not a critical schedule driver.

Tier B: Prosumer and professional ECAD (best for strong interactive routing)

- Tools like Altium shine when you have designers who can route quickly using interactive features and constraint systems. Assisted routing can reduce effort, but you are still guiding the process. Altium’s own documentation is clear that some automation features are guided interactive routing rather than full autorouting.

Best fit: moderate complexity, teams that value a unified environment and strong manual control, and schedules that can absorb polishing time.

Tier C: Enterprise routing stacks (best for sophisticated constraints, complex organizations)

- High-end router ecosystems can do a lot when rules are mature, libraries are clean, and teams know how to drive the tooling. They are often expensive, and the productivity gains depend heavily on process maturity.

Tier D: AI-powered layout systems (best for reducing cycle time and increasing iteration)

- If your actual problem is “layout is the rate limiter,” AI-driven candidate generation can change the economics. Quilter supports common enterprise and open workflows: its Quickstart documentation lists supported CAD file formats including Altium, KiCad, Cadence Allegro, and Siemens Xpedition.

Best fit: dense and constrained boards, high iteration pressure, and teams that want to keep engineers focused on architecture, review, and bring-up instead of routing volume.

A quick mapping from board type to tool approach

Simple MCU boards (2-layer)

If you are routing a basic microcontroller board with relaxed constraints, almost any modern tool can get you there. Your deciding factor is usually cost and comfort.

Moderate mixed-signal (4-layer)

This is where “best autorouter software reviews” start to diverge from reality. The board is not impossible, but cleanup time balloons. Guided interactive routing can work, but it often becomes a craftsmanship task. AI-driven workflows start to show meaningful wins here because they reduce the manual tail.

Dense high-speed and RF (6 to 12 layers)

If you are routing DDR, PCIe, impedance-controlled nets, or RF keepouts, schedule risk often comes from repeated rework and tuning. In Quilter’s published benchmark, the biggest gains showed up on the complex DDR plus PCIe plus RF board class, not the easy board.

This is the zone where “generate multiple candidates and validate” is more robust than “route once and hope.”

What Results Can You Expect from Quilter vs. Traditional Tools?

You can expect two outcomes to change when moving from traditional autorouting to AI-driven layout: time-to-routing and manual cleanup effort. The third outcome, which matters just as much, is how many viable options you can explore before you commit to a design.

Before the table, an important note: completion rates and cleanup effort are highly dependent on constraints quality, placement quality, and how disciplined your team is about rules. Treat ranges as practical expectations, not guarantees.

Side-by-side comparison

<table> <thead> <tr> <th>Solution</th> <th>Routing Technology</th> <th>Typical Completion Rate</th> <th>Manual Cleanup Effort</th> <th>Best Fit</th> </tr> </thead> <tbody> <tr> <td>Quilter</td> <td>Physics-driven AI, RL-based candidate generation</td> <td>90-99% on complex boards (when constraints are defined)</td> <td>Minimal to low</td> <td>High iteration pressure, dense constraints, teams reducing layout as a bottleneck</td> </tr> <tr> <td>Altium Designer</td> <td>Interactive routing, push-and-shove, guided assisted routing</td> <td>60-80% on moderate boards (varies widely)</td> <td>Moderate</td> <td>Strong interactive workflows, teams with experienced operators</td> </tr> <tr> <td>Cadence Allegro (Router ecosystem)</td> <td>Advanced shape-based routing with extensive constraint systems</td> <td>70-90% on dense boards (process-dependent)</td> <td>Moderate to high</td> <td>Enterprise environments with mature rules, libraries, and routing specialists</td> </tr> <tr> <td>KiCad + FreeRouting</td> <td>Open-source interactive routing plus external rule-based autorouting via DSN</td> <td>50-70% on simple boards</td> <td>High</td> <td>Budget-sensitive teams, simpler layouts, learning and prototyping</td> </tr> </tbody> </table>

What the real benchmark data shows (Quilter vs Altium vs KiCad)

Quilter published a head-to-head benchmark across three board types, reporting time-to-route and post-route manual adjustments for Quilter, Altium Designer, and KiCad. The results are directionally consistent across board classes: Quilter required substantially less time and fewer manual adjustments, with the largest separation on the complex RF plus high-speed board.

Here is the practical way to interpret that data:

- Speed is not just “the router is faster.” It’s that the workflow reduces the number of human interventions required to get to a reviewable state.

- Cleanup is the real tax. The benchmark shows post-route adjustments dropping significantly when the layout starts from a physics-aware candidate rather than a conventionally routed baseline.

- Complexity amplifies differences. The more constraints you have, the more expensive it is to iterate manually. That’s why the biggest gains show up on the hardest boards.

A concrete case example: Project Speedrun (what “engineering bandwidth” looks like)

In Quilter’s Project Speedrun, a single engineer designed a working computer using Quilter’s physics-driven AI in under one week, with Quilter reporting 38.5 hours of human input replacing 428 hours of estimated manual effort. Quilter runtime for placement plus routing plus physics validation was reported as 27 hours, with routing completion at 98%.

That is the core ROI story for AI PC B layout in 2026: not that it replaces engineering judgment, but that it compresses low-leverage effort so you can spend more time on architecture, review, bring-up, and iteration.

Here’s How You Can Integrate Quilter Into Your Workflow

The easiest adoption path is to treat Quilter as a layout acceleration layer, not a replacement for your ECAD environment. You keep your existing CAD tools for schematic capture, final DRC, documentation, and fabrication outputs. Quilter sits in the middle where schedule pain usually lives: placement and routing throughput.

Quilter’s Quickstart guidance is explicit about what you need up front: a complete schematic and a supported CAD file format. It lists support for Altium, KiCad, Cadence Allegro, and Siemens Xpedition.

From there, the workflow looks like this:

- Prepare your project and constraints

Start with a clean schematic and a linked board file. Define what must not change: board outline, connector placement, keepouts, layer count, and any critical routing intent like diff pairs or impedance targets. - Upload your native project

Instead of exporting to a fragile intermediate format, you submit the project in the environment your team already uses. The goal is low friction: use the same source of truth you will use for signoff. - Review detected constraints and intent

A major differentiator for AI-driven layout is that it can surface what it believes the design requires. For example, Quilter has described automatic detection and handling of differential pairs, including impedance-aware calculations and stack-up-specific routing based on physics modeling. - Generate multiple candidates in parallel

This is where the workflow stops behaving like a classic autorouter. Rather than producing one best-effort result, you get multiple complete candidates to compare, each evaluated against constraints. - Select, polish, and export back to your CAD

Once you pick a candidate, you can run your normal signoff process: DRC, silkscreen cleanup, fab notes, and any final tuning.

Visual workflow diagram

<pre> Schematic + Constraints | v Upload native ECAD project | v Constraint + intent review (keepouts, diff pairs, impedance, stack-up) | v Parallel candidate generation + physics checks | v Select best candidate | v Export back to native ECAD for final DRC + fabrication outputs </pre>

Ready to See Faster, Smarter PCB Layout?

If your team is still treating layout as a slow, serial step, 2026 is a good year to change that. Traditional autorouters can help in narrow lanes, but AI PCB layout workflows are increasingly the best way to reduce routing time, increase completion confidence, and get more design iterations without hiring more routing bandwidth. Start by trying Quilter on a real board, compare the candidate outputs to your current flow, and decide based on what matters most: speed, quality, and how quickly you can get to a build-ready design. For next steps, explore the Product pages, Workflow overview, and Support resources on the Quilter site, or request a demo tailored to your board class and constraints.