Read the Full Series

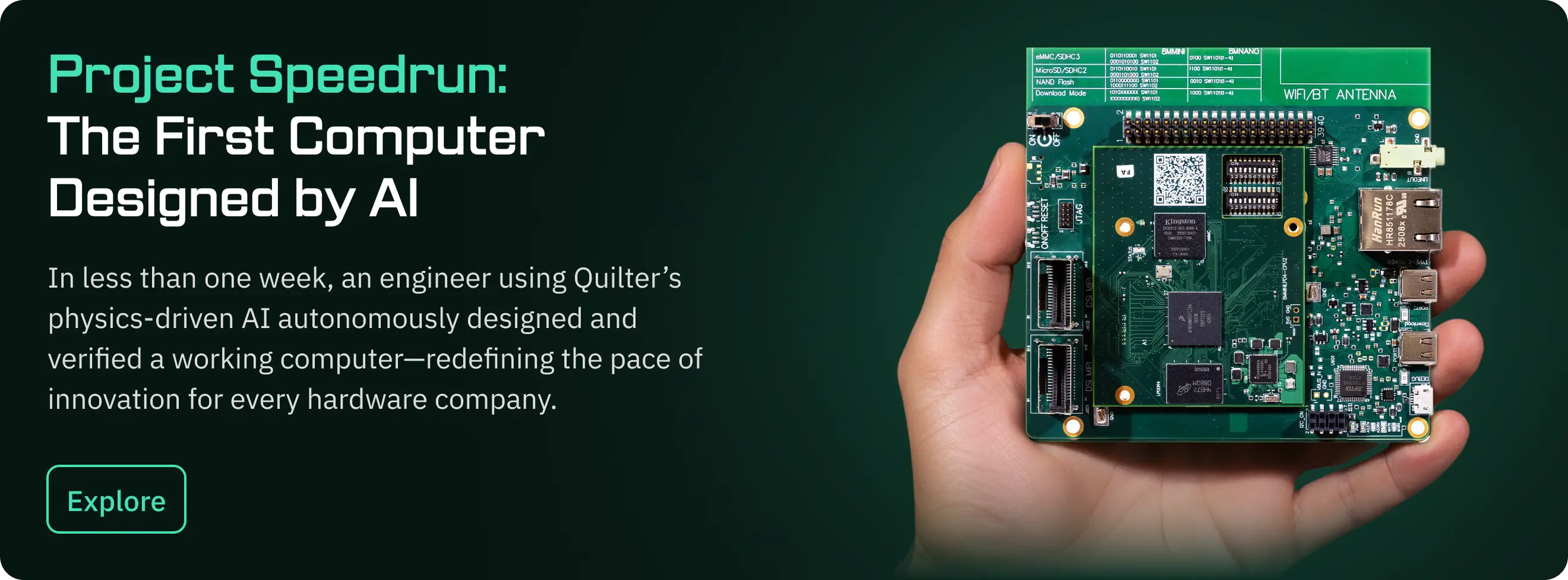

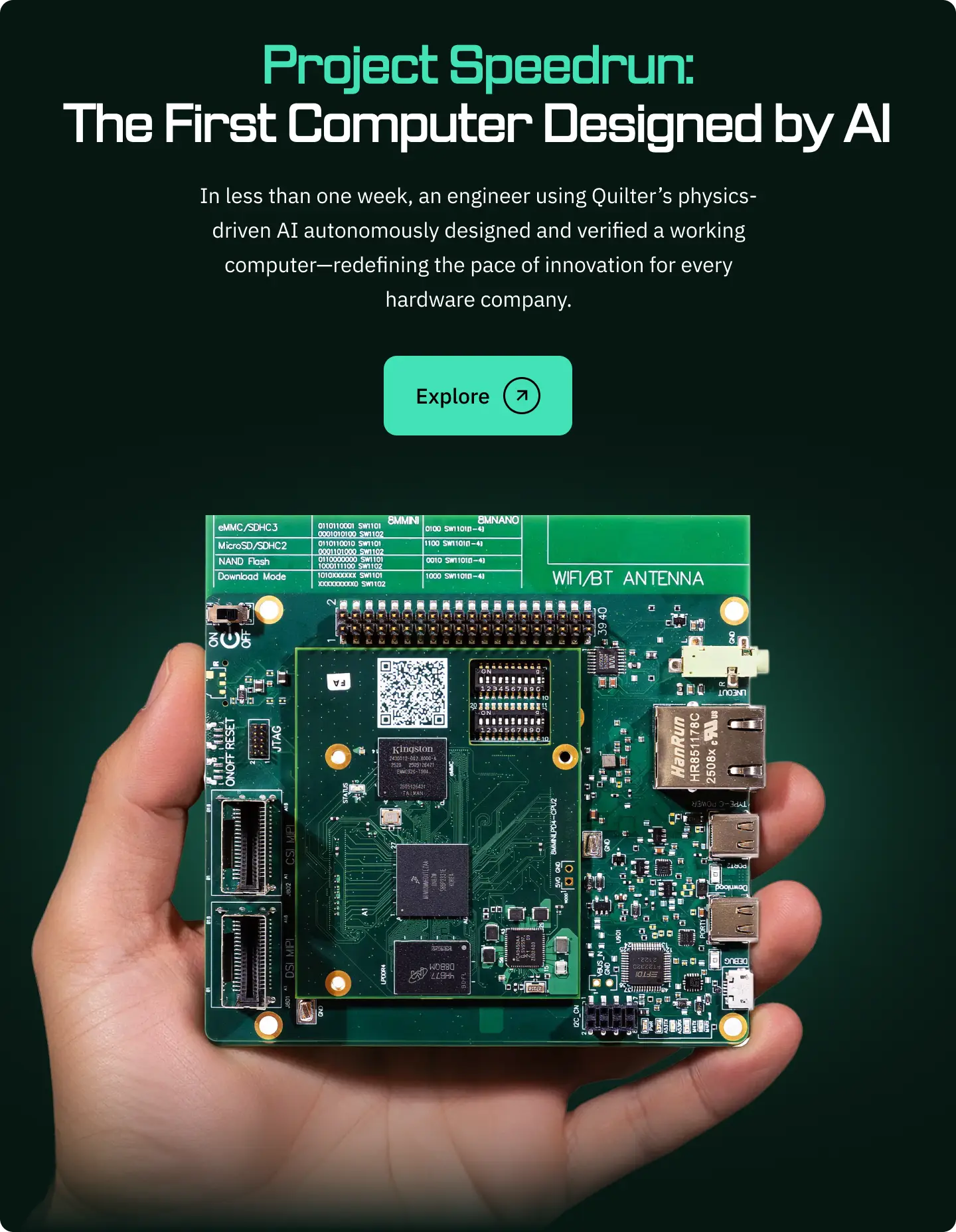

This article is one part of a walkthrough detailing how we recreated an NXP i.MX 8M Mini–based computer using Quilter’s physics-driven layout automation.

Most conversations about automated routing software still assume a lone PCB designer, a desktop CAD session, and a lot of manual cleanup after the autorouter finishes. That is not how modern hardware teams build anymore. In 2026, the question is not just which PCB autorouting tool can connect traces.

The real question is which routing approach helps your team move faster, validate more designs, and get better boards to the lab with less wasted effort.

Quilter’s own product and positioning make that distinction clear: it is built to generate multiple candidates in hours, validate them against physics, and return results in the same CAD formats teams already use.

Quick comparison: interactive routing vs classic autorouters vs physics-driven AI

Approach

Best for

Typical workflow

Main limitation

What modern teams get

Interactive routing

Critical nets, final polish, expert-driven layouts

Designer routes inside CAD, net by net or region by region

Still heavily dependent on scarce expert time

High control, but low layout abundance

Classic PCB autorouting

Simpler boards or narrow routing tasks

Rules configured up front, autorouter runs once, designer cleans up output

Often brittle on dense, high-speed, or fast-changing designs

Some speed-up, but limited trust and parallel exploration

Physics-driven AI layout

Test, validation, eval, interconnect, and fast-turn boards

Team uploads existing CAD project, defines constraints, generates multiple validated candidates

Requires a new workflow mindset, not just a button click

More candidate boards, faster iteration, physics-aware review

Benchmark callout

Test fixtures and harnesses: shave 4 to 6 weeks off board bring-up

IC evaluation boards: layout cycles cut from weeks to hours

Backplane and interconnect boards: 30+ days to under 24 hours

Let’s define what “modern” really means for hardware teams in 2026

A modern hardware team is not just a team using newer software. It is a team operating under very different constraints.

In practice, that means distributed engineers, tighter handoffs between EE, PCB, firmware, mechanical, validation, and manufacturing, and a much shorter window between schematic intent and lab reality.

It also means more board variants, more validation hardware, and more pressure to learn quickly rather than betting everything on a single layout pass.

Traditional routing tools were built for a different world.

They assumed a mostly single-user desktop workflow in which one experienced designer held most of the layout context, requirements were relatively stable, and routing was treated as a geometry exercise within a single CAD environment.

That model still exists, but it no longer matches how fast-moving semiconductor, robotics, consumer, and aerospace teams actually work.

For modern hardware teams, routing is not just a design task. It is a throughput problem and a coordination problem.

If the layout is slow, validation slows down as well. If validation slows down, the firmware waits. If firmware waits, program risk climbs.

The routing bottleneck compounds across the whole development loop.

That is why good automated routing software in 2026 has to do more than push traces around. It has to fit into a broader system of collaboration, review, verification, and iteration.

It has to work with PLM, existing CAD tools, multiple stakeholders, and a team that wants more layout options, not just one routed board, a bit sooner.

Here’s why classic autorouters struggle with today’s boards and teams

Classic PCB autorouting was built around a narrow assumption: define the rules well enough, press go, then inspect the result. On paper, that sounds efficient. In real programs, it often breaks down.

The first issue is that traditional autorouters depend on stable, complete, high-quality constraints up front. But real programs are rarely that clean.

Connector placement changes. Board outlines move. Stack-ups evolve. Critical nets get reprioritized. Mechanical realities show up late.

A single-shot routing run does not adapt gracefully to that kind of churn.

The second issue is output quality. Experienced teams know the failure modes: ugly via forests, questionable return paths, power integrity trouble, awkward escapes, traces that are technically connected but hard to trust, and harder to review.

Many teams discover that tuning the autorouter, rerunning it, and cleaning the results can take longer than doing the important routing interactively in the first place.

There is also a team-level limitation. Many legacy routing environments are still constrained by seat-based licensing and designer-centric workflows.

That creates friction when more people want to participate in layout decisions, review alternatives, or evaluate candidate boards in parallel.

That is the mismatch.

Modern teams need rapid iteration, more variants, and faster learning loops. Legacy autorouters generally assume one run, one user, one CAD session, and one answer.

That is not enough for boards and organizations that change by the day.

What should automated routing actually do for your team today?

The wrong way to evaluate automated routing software is to ask whether it can replace every human routing decision. The better question is whether it increases useful engineering output.

For a modern hardware team, success looks like more validated boards built per month. It looks like more candidate layouts are explored before you commit. It looks like earlier feedback on physical constraints.

It looks like designers are spending their time on floorplanning, critical nets, architectural trade-offs, and reviews, rather than manually shepherding every single connection across the board.

That changes what matters.

Automated routing should enforce real physical constraints, not just cosmetic neatness. It should handle impedance-controlled nets, differential pairs, bypass capacitor treatment, manufacturability constraints, and reviewable design intent.

It should provide enough layout detail that teams can compare stack-ups, board outlines, manufacturers, or placement strategies instead of betting everything on one path.

It should also improve collaboration. Modern hardware teams need machine-readable constraints, shareable candidate layouts, transparent review states, and outputs that slot back into the tools everyone already knows.

Routing automation should reduce hidden work, not create a black box that only one specialist can interpret.

That is the core reframing: automated routing software should not be judged as a neat CAD feature.

It should be judged as PCB layout automation that increases throughput, improves confidence, and frees scarce experts to work on what actually differentiates the product.

Here’s how the main routing tool categories stack up now

The current market breaks into a few clear categories.

Enterprise EDA autorouters like Cadence Allegro X, Siemens Xpedition, and Zuken sit at the high end. They are powerful, mature, and deeply embedded in large organizations. They are often the right answer for very complex design environments, especially when tied into broader SI, PI, and manufacturing workflows.

But they are also heavyweight, heavily specialized, and still largely organized around a human doing most of the actual layout work inside the CAD session.

Mid-market design tools like Altium Designer, PADS Pro, and Fusion 360 offer strong interactive routing and a more accessible user experience for many teams. They are often excellent day-to-day environments for design capture, layout, and final signoff.

But even when they include autorouting capabilities, the workflow is still designer-centric. They help a skilled user work faster. They do not fundamentally change the number of candidate boards a team can evaluate.

Open-source paths like KiCad plus external autorouters are attractive on cost and flexibility. For startups, research groups, and budget-sensitive robotics teams, that can be a real advantage. The tradeoff is that high-speed work, advanced constraints, and workflow consistency often require more manual expertise and setup.

Newer cloud and AI-assisted environments are pushing the market toward collaboration and faster iteration. They matter because they reflect where the industry is going. But many of these tools are still earlier in the maturity curve for dense, highly constrained, or regulated hardware programs.

That is the important anchor point for buyers searching “top automated routing software for modern hardware teams.” Most options in the market still assume the human is doing most of the layout work inside a CAD session.

They may route faster. They may collaborate better. But they are not all solving the same problem.

How is physics-driven AI routing different from a “smart” autorouter?

This is where Quilter sits in a different category.

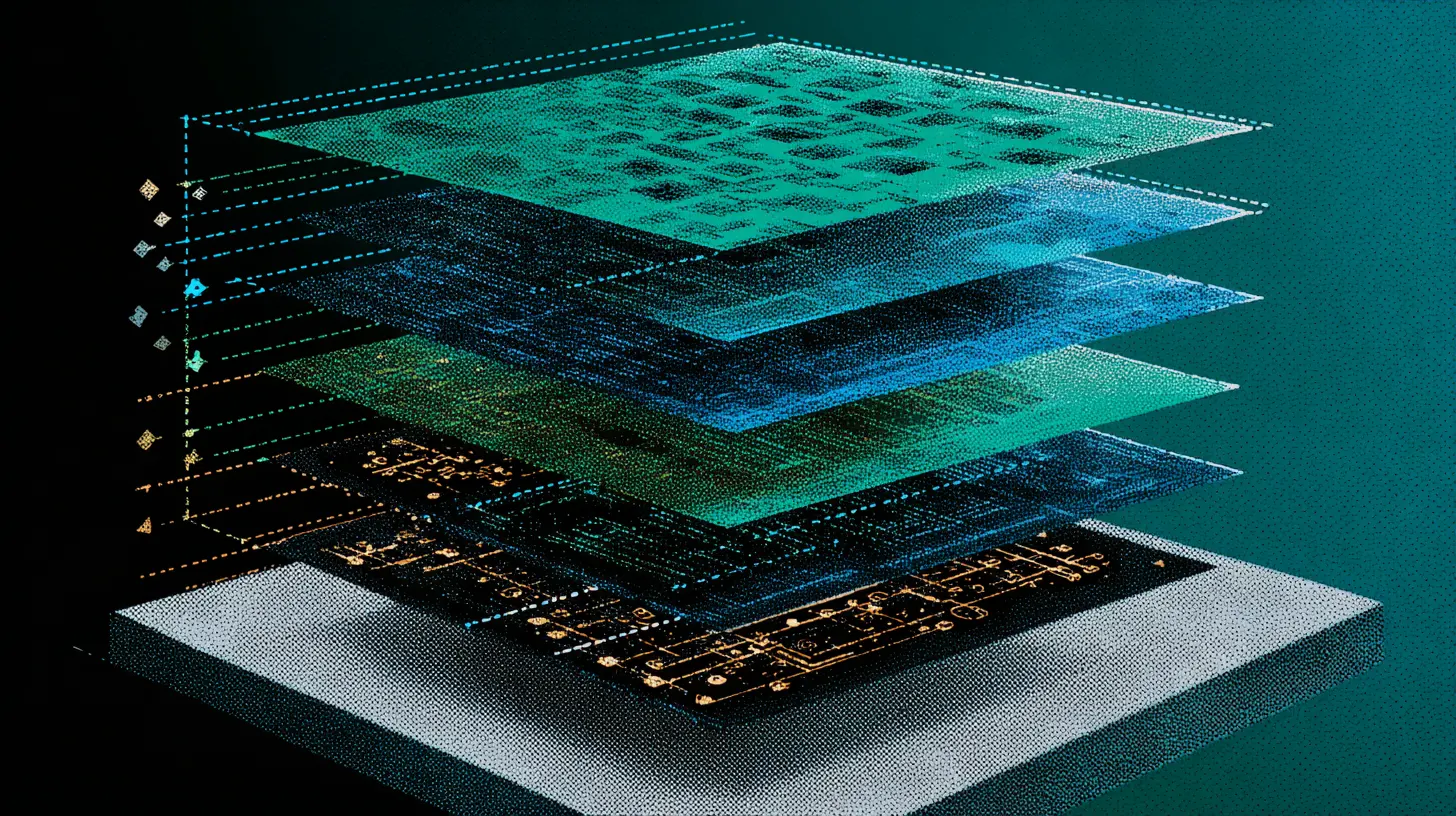

Quilter is not just a smarter version of the old autorouter model. Based on the provided company context, Quilter uses reinforcement learning to explore thousands of candidate boards, generate multiple layouts in hours, and evaluate them against physical constraints before handing results back to the team.

It is explicitly positioned as physics-driven AI for electronics design, not just automated trace connection.

That matters because single-shot rule execution and active exploration are not the same thing.

A classic autorouter mostly follows predefined routing logic and hopes the result is workable. Quilter’s approach is to search a much larger design space, identify context such as bypass capacitors, impedance-controlled nets, and differential pairs, and then produce candidate boards for review against the stated constraints.

The result is closer to automated layout generation than traditional PCB autorouting.

Just as important, the review model is different.

Quilter describes transparent design review, where teams can see what the system will and will not account for, and evaluate which aspects of a design are truly done versus still needing human attention.

That is a much more practical model for senior engineers and PCB designers who need both speed and accountability.

Industry vignette: semiconductor

A semiconductor validation team has an eval board blocking silicon bring-up. In a traditional flow, the board sits in a layout queue while firmware and test teams wait.

In a physics-driven AI flow, the team can generate candidate layouts quickly, review the strongest options, and get a board toward fab without burning weeks on backlog.

Industry vignette: robotics

A robotics startup needs multiple revisions of a motor-control support board as enclosure constraints and connector choices keep moving.

Instead of treating every change as a near-full layout restart, the team uses PCB layout automation to explore options in parallel and keep integration moving forward.

Where Quilter fits in a stack with Altium, Cadence, Siemens, and KiCad

One of Quilter’s most practical strengths is that it does not ask teams to throw away their existing stack.

According to the provided materials, teams can upload Altium, Cadence, Siemens, or KiCad projects directly, define the board outline, pre-place connectors and critical components, set the floorplan and constraints, then receive output back in the same native format.

That makes adoption easier because Quilter is additive. It sits between your design intent and your final manufacturing handoff.

Existing CAD project

(Altium / Cadence / Siemens / KiCad)

|

v

Constraint setup

board outline, floorplan,

pre-placed critical parts

|

v

Quilter

physics-driven AI layout

multiple candidates

transparent review

|

v

Native CAD output returned

|

v

DRC, final edits, fab files,

manufacturing handoff

For a semiconductor team, that might look like Allegro plus Quilter for validation and test hardware. For a consumer electronics team, it could be Altium plus Quilter to accelerate rapid-turn boards ahead of a launch window.

For a startup using KiCad, it can mean getting access to reinforcement learning routing and physics-driven AI layout without abandoning the toolchain the team already knows.

For enterprise buyers, that integration story matters even more. Quilter’s context explicitly references mission-critical environments, including aerospace and defense, and supports secure in-house innovation and compliance-sensitive work.

Explore the stack further: Product, Technology, Solutions, Pricing

Try it on a real project

Upload an existing Altium, Cadence, Siemens, or KiCad project and see how many physics-validated candidates your team can review in a single workday.

Industry vignette: consumer electronics

A consumer device team is racing toward an EVT deadline.

The schematic is ready, the industrial design is moving, and everyone knows a slow layout cycle could blow the schedule.

Rather than wait for a single perfect routed board, the team uses automated routing software to generate candidates quickly, then narrows down to the best option with human review.

Industry vignette: aerospace and defense

A defense program needs a validation board under tight schedule pressure, but cannot afford weak reviewability or last-minute physical surprises.

The appeal is not just speed. It is speed plus transparent constraint-aware review inside an existing controlled workflow.

What results can you expect when you shift routing to Quilter?

The headline numbers are strong because the workflow change is significant.

Quilter positions itself around schematic-to-fab-ready in under 4 hours, with first candidates often appearing within the first hour and bring-up-ready boards arriving in a single workday for several industry use cases.

It also highlights design-type benchmarks such as cutting test fixture bring-up by 4 to 6 weeks, reducing IC evaluation board layout cycles from weeks to hours, shrinking design validation cycles from months to days, and taking backplane or interconnect work from 30+ days to under 24 hours.

Those numbers are important, but the qualitative impact may matter even more.

Teams get more variants to compare. They find issues earlier. PCB designers spend less time buried in repetitive routing labor and more time on the subtle judgment calls that actually require expertise.

Validation engineers get hardware sooner. R&D managers get more throughput without adding proportional headcount. That is why Quilter belongs in the conversation around top automated routing platforms for modern hardware teams.

It is not just promising a cleaner autorouter. It is promising a higher-output development loop.

Here’s how to pilot automated routing in your team over the next 30 days

A good pilot does not need to be risky or political. Keep it practical.

Start with one board that matters but does not carry maximum organizational anxiety. A test fixture, IC evaluation board, design validation board, or interconnect board is ideal. Those are also exactly the categories Quilter already emphasizes.

Define the board outline, floorplan, critical placements, and constraints clearly.

Then run Quilter in parallel with your standard layout process.

From there, compare outcomes on a few metrics that matter:

- Time to first usable candidate

- Number of viable layout options produced

- Review the effort required from the PCB and EE teams

- DRC and manufacturability readiness

- Lab bring-up performance and late-stage surprises

Make the evaluation cross-functional. PCB designers should judge reviewability and cleanup effort. Validation engineers should judge whether earlier hardware access changes the program. R&D managers should look at cycle time and team throughput.

That gives you a real answer, not just a tool demo impression.

The pricing model matters here, too. Quilter’s provided context says pricing scales by pin count, not seats, which removes one of the usual adoption bottlenecks.

More people can participate in the evaluation without fighting over licenses.

30-day pilot checklist

- Pick one upcoming board: test fixture, eval board, validation board, or interconnect

- Export or upload the existing Altium, Cadence, Siemens, or KiCad project

- Define board outline, pre-placed critical components, and key constraints

- Run Quilter in parallel with your usual layout flow

- Compare time-to-first-candidate and number of viable options

- Review outputs with PCB, EE, validation, and R&D stakeholders

- Check DRC, manufacturability, and lab readiness

- Decide whether the gain is routing speed alone or broader team throughput

- Expand next to a second board type if the pilot proves out

For teams evaluating automated routing software in 2026, that is the real test. Not whether the tool can draw traces, but whether it gives your team a better development loop.

If you want to see where physics-driven AI layout fits in your own stack, start with an existing Altium, Cadence, Siemens, or KiCad project and generate your first routed candidates in a single workday.

Quilter is built to work with the tools you already use, while changing the part of the process that still costs hardware teams the most time.