Read the Full Series

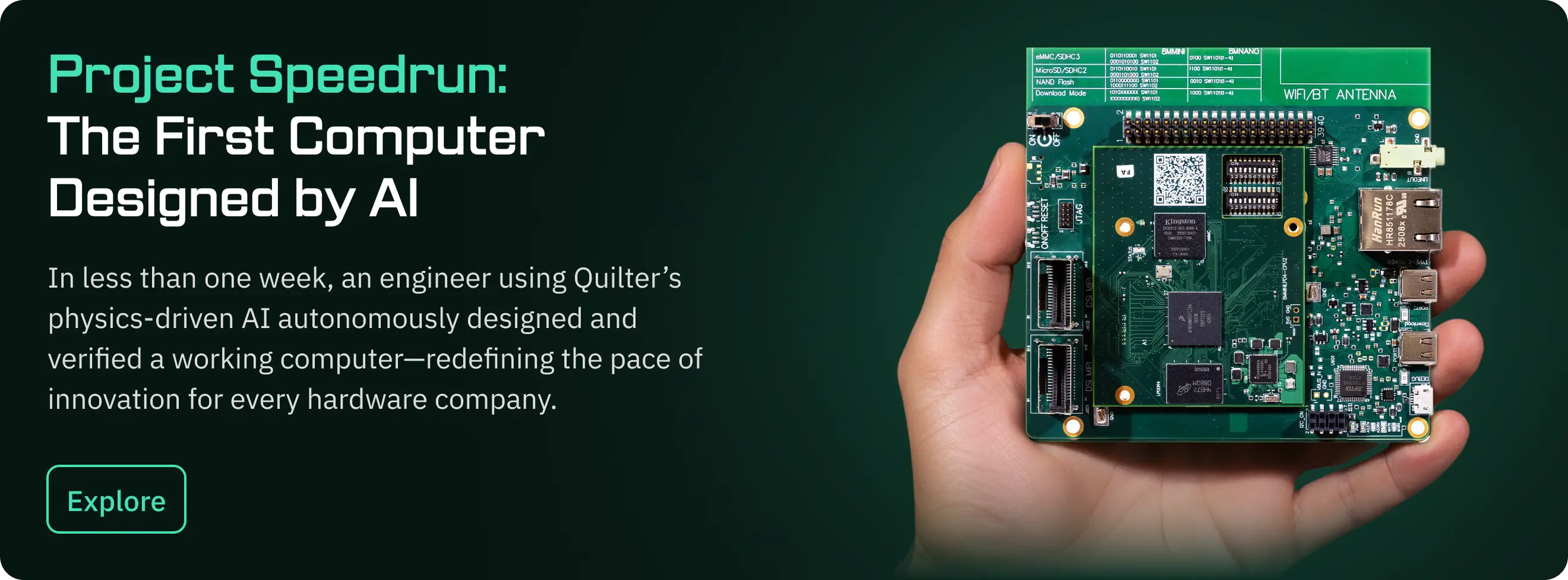

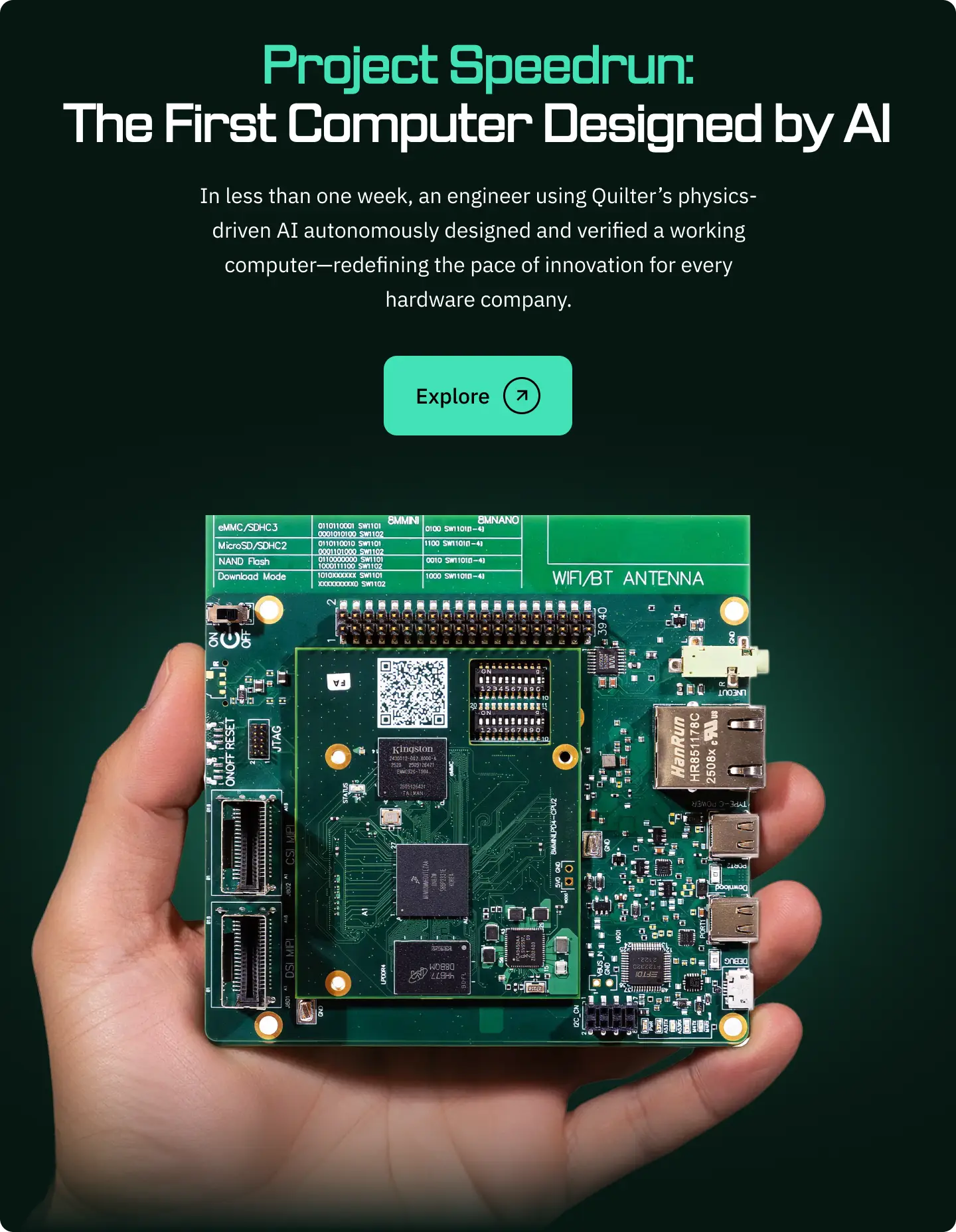

This article is one part of a walkthrough detailing how we recreated an NXP i.MX 8M Mini–based computer using Quilter’s physics-driven layout automation.

If you ask, “What are the best automated PCB routing tools on the market right now?”, you usually get the same shortlist: Allegro, Xpedition, Altium, KiCad, plus FreeRouting, maybe a few newer AI-flavored platforms. That answer is not wrong. It is just incomplete.

In 2026, there are really two different conversations hiding inside that one question.

The first is about classic PCB autorouter technology: tools that help route a board faster when a skilled engineer sets up the right constraints, chooses the right corridors, and closely supervises the result.

The second is about a newer category entirely: AI PCB routing systems that do not just follow rules net by net, but explore full-board outcomes and evaluate them against physical behavior.

That distinction matters because the real question is not “Which PCB autorouter exists?” It is “Which routing workflow gets me to a fabrication-ready board faster, with fewer ugly compromises, less manual cleanup, and more confidence when the board hits the lab?”

That is where Quilter belongs in a different category.

Quilter uses reinforcement learning to generate multiple candidate layouts in hours, applies a physics design review to those candidates, and returns files in the same CAD environment your team already uses.

In other words, it is not just another automation feature inside a legacy layout package. It is a different operating model for routing itself.

Let’s define what people mean by “automated PCB routing” today

“Automated PCB routing tools” is a broad phrase, and engineers often use it to describe very different things.

Sometimes they refer to interactive routing features such as push-and-shove, glossing, neck-down assistance, or guided differential pair handling.

Those features are valuable, but they are not full autorouting. They are designer-in-the-loop productivity tools.

Sometimes they mean batch autorouting, where a PCB autorouter is asked to complete whole sections of the board based on a set of cost functions and design rules.

This is where the old reputation comes from.

Engineers remember spaghetti routes, too many vias, awkward detours, and long cleanup sessions afterward.

Sometimes they mean sketch routing or corridor-based routing, where the engineer still defines the intent and the software fills in the geometry.

Tools like this can be very productive, especially on buses and mid-complexity boards.

And now, increasingly, they mean full AI PCB routing: systems that can take a design, understand board-level constraints, generate multiple complete candidates, and deliver layouts worth reviewing rather than messes worth rescuing.

That is why the market feels confusing. Allegro and Xpedition still matter. Altium still matters. KiCad plus FreeRouting still matters.

But Quilter sits in a separate category from all of them: physics-informed routing that can own the entire routing task for many board types, rather than acting as a cleanup assistant for the human.

That is a very different promise, and for the right board, a much more meaningful one.

What really makes one routing tool “the best” for a given board?

There is no universal winner because boards are not all alike.

A four-layer control board with relaxed timing is not the same problem as a dense FPGA design, a validation board, or a backplane carrying high-speed interfaces.

The best PCB routing tools for one class of work may be the wrong choice for another.

In practice, teams judge routing tools on a handful of criteria that matter far more than marketing claims.

First, can the tool handle the board's actual complexity?

Layer count, BGA density, controlled-impedance nets, differential pairs, return-path behavior, power-integrity concerns, and manufacturing limits all shape what “good” looks like.

Second, what is the quality of the result? Not just “did it connect all the nets,” but how many vias it used, how readable the topology is, how clean the fanout looks, how well congestion is managed, and whether the board is maintainable when ECOs arrive.

Third, how much setup work is required before the tool saves time? A PCB autorouter that takes hours of expert constraint tuning before it becomes helpful may still be the right choice in a mature enterprise flow.

But for many teams, setup costs quietly eat up the time savings they were hoping to get back.

Fourth, how much expert attention does the workflow demand? Some tools are powerful only when a very strong designer is constantly steering them.

Others reduce the amount of manual babysitting required.

That is the right lens for comparing classic autorouters against Quilter AI.

The point is not raw automation. The point is routing quality, cycle time, review burden, and the amount of senior engineering time required to reach a board you trust.

Here’s how classic autorouters behave on real boards

Traditional autorouters generally optimize local routing decisions using rule-driven cost functions.

Depending on the tool, that may involve maze routing, grid-based search, shape-based expansion, push-and-shove logic, or a combination of methods layered on top of one another.

This can work well enough on simpler boards or tightly bounded sections of a larger design. It can even work very well when the human lays out the floorplan carefully, routes critical nets first, aggressively constrains the remaining problem, and uses the autorouter sparingly.

That is why many experienced designers still keep these tools in the toolbox.

But the weak spots are familiar.

On real boards, a classic PCB autorouter often optimizes for completion more than elegance.

That leads to tangled paths, unnecessary vias, awkward escapes under dense packages, inconsistent route structure, and boards that technically pass rules while still looking like they will be painful to debug or modify later.

The limitation is not that these tools are useless. It is that most of them do not reason about the board the way an experienced designer does.

They follow rules. They do not truly understand board-level physical tradeoffs.

Take a 10-layer FPGA board as a simple scenario. A good engineer will usually hand-route memory, SerDes lanes, clocks, and the most sensitive power or return-path situations. Then the autorouter might be turned loose on lower-speed I/O and cleanup work.

That workflow exists for a reason.

Teams do not trust the classic autorouter to make the highest-consequence decisions on its own.

That is also why the reputation of autorouters has stayed mixed for so long. They can save time, yes.

But they often save time only when used selectively, and only after the engineer has already solved the hardest part of the layout.

How does physics-informed AI routing change the game?

Physics-informed routing changes the problem from “How do I connect these nets while obeying rules?” to “How do I generate strong full-board outcomes under electrical, physical, and manufacturing constraints?”

That is the core shift.

Quilter uses reinforcement learning to explore many candidate boards rather than committing early to a single path and then pushing forward.

Instead of treating routing as a collection of isolated net-level decisions, it evaluates layout quality at the board level.

That matters because boards succeed or fail as systems, not as a pile of individually legal traces.

The practical result is a different kind of output.

Quilter is designed to account for the things engineers actually care about during review, including bypass-capacitor handling, impedance-controlled nets, differential pairs, and other critical physical considerations called out up front.

It generates multiple candidates in hours, then evaluates them through a physics-based design review rather than relying solely on DRC.

That is what makes Quilter AI more than a modernized PCB autorouter. A classic autorouter may give you something routable.

Quilter aims to give you candidate layouts that look more like the work of an experienced designer: cleaner topology, more sensible via usage, better-structured escapes, and fewer obvious signs that the software simply chased completion.

Just as important, the engineer does not disappear from the process.

Your team still controls the board outline, pre-placement, floorplan, constraints, stack-up choices, and final sign-off. Quilter fits into the native CAD workflow your designers already know, returning files in the same format they started with.

That significantly lowers the adoption barrier, especially for organizations that cannot afford a toolchain migration just to test a new routing approach.

Where do leading EDA autorouters still make sense in 2026?

A balanced answer has to say this clearly: leading traditional autorouters still make sense in a lot of workflows.

Cadence Allegro, Siemens Xpedition, and Zuken remain strong options when teams operate in deeply specialized, highly mature environments with experienced layout engineers, entrenched constraint systems, and flows built around those platforms.

In those settings, the combination of interactive tooling, batch routing assistance, and ecosystem integration can still be the right call.

Altium remains useful, especially when guided or semi-automatic routing is sufficient. Many teams do not need a fully autonomous system for every board.

They need a fast, capable assistant who can help with buses, repetitive structures, or tedious but not especially risky portions of the board.

KiCad, FreeRouting, and niche options like TopoR also have a place.

They are attractive when the budget is tight, when the board is moderate in complexity, or when the team wants an accessible way to automate part of the routing task without the overhead of enterprise software.

The common theme is this: classic autorouters work best when a strong human is still doing a lot of the strategic thinking.

That is where Quilter becomes complementary rather than ideological.

You do not have to replace your CAD environment, your review habits, or your enterprise design process. You can keep the tools you already trust and use Quilter when schedule pressure, bandwidth limits, or board volume make full manual routing too time-consuming.

How does Quilter’s AI stack up against tools like FreeRouting and enterprise autorouters?

The cleanest way to compare these categories is to judge them on the criteria engineers actually care about.

Tool category

Routing quality

Setup burden

High-speed awareness

Iteration speed

Required expertise during routing

Quilter AI

High, designed for full-board candidate quality and physics review

Moderate

Strong emphasis on critical physical constraints

Very fast, multiple candidates in hours

Lower ongoing babysitting, engineer reviews candidates

Allegro / Xpedition

High in expert hands

High

Strong, especially inside mature enterprise flows

Moderate

High, depends heavily on expert steering

Altium guided routing

Good on mid-complexity work

Moderate

Good for guided flows, less suited to hardest cases

Moderate

Moderate to high

KiCad + FreeRouting

Variable

Low to moderate

Limited for demanding high-speed work

Fast to try, slower to clean up

Moderate, often cleanup-heavy

That table tells the real story. FreeRouting comparison conversations often focus on cost because FreeRouting is accessible.

But cost is only one variable.

The better question is how much engineer time gets burned on setup, supervision, cleanup, and review before a board is actually ready to move forward.

Imagine the same 8 to 10-layer mixed-signal board routed in two ways. In a FreeRouting-style flow, you may get a board that completes, but with more vias, less elegant path structure, and escapes that require substantial inspection and refinement.

In a Quilter flow, the expectation is not just completion. It is cleaner fanout, more consistent via distribution, straighter and more readable paths, and candidates filtered through a physics design review, so weak layouts are less likely to survive just because they passed rule checks.

That does not mean enterprise teams should throw out tuned Allegro autorouter or Xpedition flows. In some organizations, those flows are sophisticated and highly optimized.

But even there, Quilter can be useful as a fast exploration engine. It gives teams more options earlier, which is often exactly what a time-sensitive hardware program needs.

What will your workflow actually look like with AI routing in the loop?

This is where a lot of skepticism usually fades, because the workflow is more familiar than people expect.

Start in the CAD system you already use. Quilter supports projects from Altium, Cadence, Siemens, and KiCad.

Your team exports the design, defines the board outline, pre-places the connectors and other must-fix elements, and establishes the floorplan and constraints. You stay in control of those decisions.

From there, Quilter identifies critical layout considerations for review, including bypass capacitors, impedance-controlled nets, and differential pairs.

That matters because it gives the engineer visibility into what the system will and will not account for before generation begins.

Again, this is not blind push-button automation. It is a transparent setup around the highest-consequence design requirements.

Then the AI exploration phase begins. Instead of waiting for a single layout attempt, you get multiple candidates generated in parallel, potentially across different trade-offs like stack-up choices, form factors, or strategies.

That abundance is a major advantage in workflow. It changes routing from a one-shot task into a reviewable design space.

Once the candidates are back, your designers evaluate them inside the native CAD environment.

Run DRC. Polish where needed. Check silkscreen, outputs, and fabrication details. Approve the design you want. The handoff stays inside the tools your team already knows.

That is an important operational point. Adopting Quilter does not require retraining the whole organization on a brand-new design stack.

It is a lower-friction workflow than most engineers assume when they first hear “AI routing.”

What results can you expect if you switch from an autorouter to physics-first AI?

The biggest change is cycle time.

Quilter’s positioning is clear: multiple candidates in hours, first candidates often appearing within the first hour, and full fab-ready designs in under four hours for relevant workflows.

That is a very different pace from traditional board layout cycles measured in days or weeks.

The company also frames the value in concrete board classes, including test fixtures and harnesses, IC evaluation boards, design validation boards, and backplane or interconnect boards, where schedule pressure is often severe.

For hardware teams, that speed is not just a convenience metric. It changes what is possible inside the program schedule.

More candidates mean more iterations before fabrication.

More iteration usually means better decisions. Better decisions early tend to reduce layout-induced surprises during bring-up. And when bring-up happens faster, the whole engineering organization gets time back.

There is also a bandwidth effect that matters just as much. Senior PCB designers should spend their time on critical net strategy, review, architectural trade-offs, and cross-functional problem-solving.

They should not be stuck trace-babysitting large volumes of non-core routing work if a better workflow exists.

That is why physics-informed routing is interesting even to teams that are already competent with classic tools. The upside is not only speed. It is the ability to reallocate scarce expert time toward the parts of the board that benefit most from human judgment.

Here’s how to try AI routing on a real design without changing tools

The easiest way to evaluate AI PCB routing isn't through a theoretical debate. It is with a controlled pilot.

Pick a board that is real, current, and useful, but not your highest-risk product. Validation boards, test fixtures, evaluation boards, and certain backplane projects are often strong candidates because the schedule matters and comparisons are easy to judge.

Use a simple checklist:

1. Choose a live board with clear routing pain or schedule pressure

2. Finalize the schematic and capture non-negotiable placements

3. Define board outline, preferred stack-up, and key constraints

4. Run your normal autorouter or guided-routing workflow in parallel

5. Upload the same design to Quilter

6. Compare route quality, via count, path cleanliness, and review effort

7. Move the strongest candidate into normal CAD review and lab validation

That parallel test is important because it keeps the comparison honest. Do not compare marketing claims.

Compare actual boards. Compare the amount of cleanup required. Compare how readable the layout is. Compare how quickly your team gets to something you would actually send toward fabrication.

Quilter offers enterprise, startup, and free-tier paths, with pricing that scales by pin count rather than by seats, making it easier to evaluate without committing the entire organization upfront.

And because the workflow returns files in the same format you submitted, the test does not force a toolchain change just to prove the concept.

Upload a real design to Quilter and see how physics-informed routing performs against your current PCB autorouter on the board that matters to you.