Read the Full Series

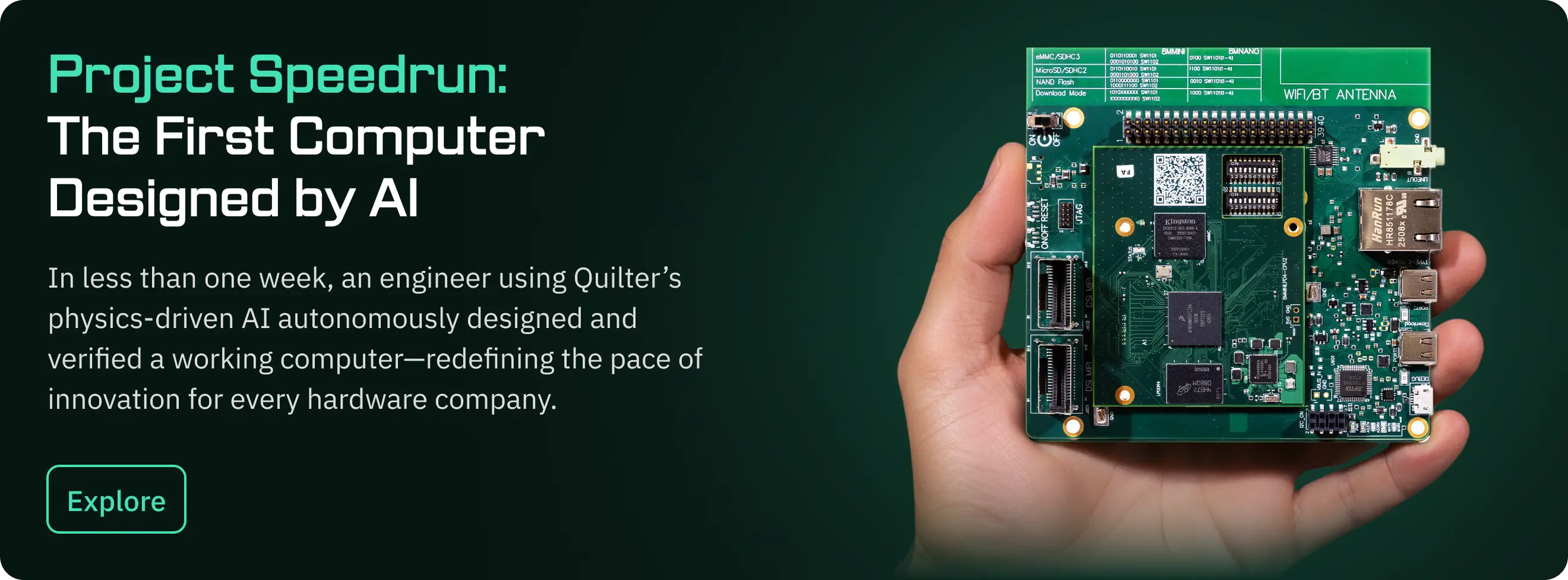

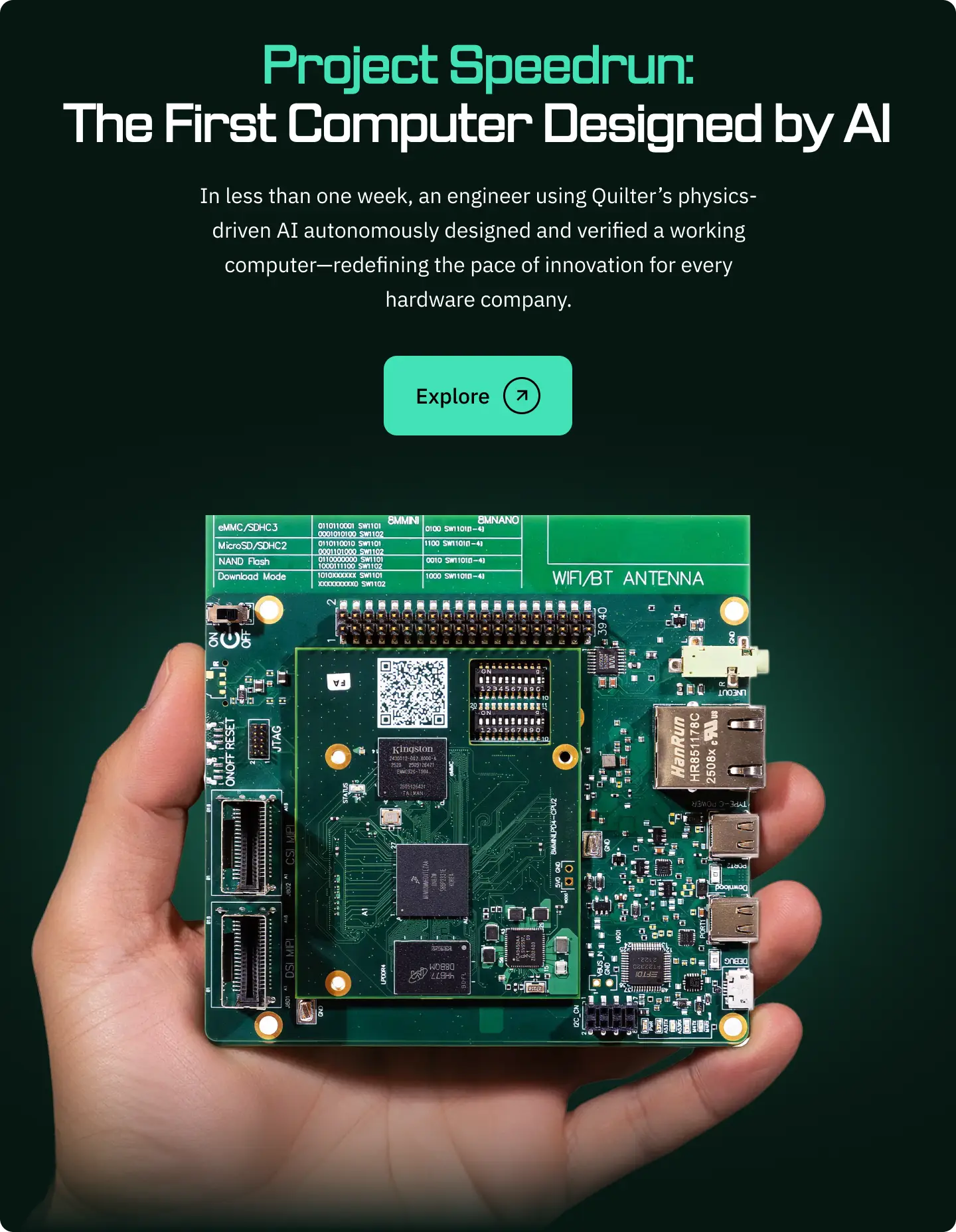

This article is one part of a walkthrough detailing how we recreated an NXP i.MX 8M Mini–based computer using Quilter’s physics-driven layout automation.

If you’re googling the best PCB design tool for startups, you’re already asking the wrong question. In 2026, the real decision is not KiCad vs Altium. It’s whether you keep treating layout as a hand-routed bottleneck or turn it into an AI-accelerated capability. This post breaks down how modern hardware teams combine traditional EDA with Quilter PCB and AI-powered PCB layout to move from schematic to boards on the bench in a fraction of the time.

Let’s talk about how hardware startups really pick their PCB tools today

Most hardware startups do not “choose the best tool.” They choose the tool that matches their runway, their hiring reality, and the board they must ship next month.

The typical path looks like this:

- Start in KiCad or Fusion because it is fast to adopt, cheap to run, and friendly for early teams that need momentum more than process perfection.

- Move to Altium as complexity grows, because the collaboration model, library workflows, and high-speed features become worth the investment once boards get dense and the team expands.

- Keep a mix of tools because prototyping, validation, and production hardware do not share the same constraints, timelines, or risk tolerance. One startup might use KiCad for early bring-up boards, Altium for the production design, and a manufacturer portal plus scripts for BOM and procurement.

What matters most is rarely a feature checklist. It is the stuff no one wants to admit in a tooling debate:

- Runway and burn. Time and payroll are the actual constraints, not whether a router has a new mode.

- Hiring pool. “Who can we hire in six weeks?” is a stronger force than “what is objectively best.”

- OS reality. If your team is split across macOS, Linux, and Windows, the choice of tool becomes organizational, not personal.

- Manufacturing partners. Your CM’s preferred formats, stackup conventions, and review expectations will quietly shape your workflow more than any marketing page.

Yes, you should acknowledge KiCad vs. Altium, Fusion, and cloud tools. But the key thing to notice is this: even teams with “the right EDA” still lose weeks to layout cycles. That is why pcb design tools 2026 conversations are shifting from editor preferences to automation level.

Here’s why the old KiCad vs. Altium debate misses the real question

The KiCad vs. Altium debate is valid. It is just incomplete.

The usual tradeoffs are familiar:

- KiCad: low cost, open ecosystem, flexible workflows, excellent for early-stage teams that can tolerate a bit of friction.

- Altium: deep feature set, polished UX, strong libraries and collaboration patterns, often the default once hardware becomes core IP and complexity increases.

But both sides share the same assumption: humans handle mostrouting and iteration manually.

That assumption is the real bottleneck for startups.

Because layout is not only “drawing traces.” Layout is:

- translating constraints into geometry

- routing and rerouting when placement changes

- managing power integrity and return paths

- resolving DRC issues while deadlines compress

- doing the same review loops again for every spin

The painful part is not that your tool cannot do it. It is that the workflow forces expensive people to spend weeks inside the loop. That creates three hidden costs:

- Human layout hours are scarce. Senior designers are scarce, and founders do not want a single person to become a throughput bottleneck.

- Context switching is expensive. Each layout iteration diverts attention from firmware, architecture, test planning, and customer milestones.

- Validation cycles slow everything. When layout takes weeks, bring-up and learning take longer, and the product narrative slows down.

So the modern framing is this:

The real choice is not “which editor is best.”

The real choice is traditional manual EDA vs AI-accelerated EDA that layers on top of the tools you already use.

That is where pcb automation for startups stops being a buzzword and becomes a survival strategy.

What should a modern PCB stack look like for a venture-backed team?

A venture-backed hardware team should think in layers. Not because it sounds neat, but because it clarifies where speed comes from.

Here is a practical 2026 PCB stack:

- Schematic capture and constraints

- Define the circuit, nets, rules, impedance targets, differential pairs, and critical constraints.

- Layout editor for placement control and final polish

- Maintain libraries, footprints, DRC workflows, and final edits.

- AI layout engine for candidate generation and routing throughput

- Generate complete layout candidates quickly, explore variations, and reduce manual routing effort.

- Simulation and validation

- Your standard checks, reviews, and sign-off expectations still apply.

- Manufacturing handoff

- Export fab and assembly files, manage DFM feedback, and close the loop with your manufacturer.

KiCad, Altium, Cadence, and Siemens are excellent at layers 1, 2, and 5. They are where engineers live for schematics, constraints, library hygiene, and final handoff.

Quilter fits after schematic and floorplanning. You upload your existing project, define the board outline and keep-outs, pre-place the components you want fixed, and specify constraints. Quilter then generates multiple complete layout candidates in hours, with physics-based review baked into the process. After that, Quilter returns files in the same formats you submitted, so you can run DRC, apply your finishing touches, and generate fab outputs in the tools you already use.

Two example stacks that match how teams actually operate:

- Pre-seed robotics startup: KiCad + Quilter + manufacturer DFM loop

KiCad remains the home for schematics and edits. Quilter accelerates layout throughput for boards that would otherwise require the team’s only experienced designer to spend weeks. - Series A consumer device team: Altium + Quilter + established DFM process

Altium remains the home for libraries, collaboration, and final sign-off. Quilter turns the layout into an abundant resource instead of a gating function.

If you want a one-sentence takeaway for evaluators:

Your EDA tool is still your system of record. AI is your throughput multiplier.

Here’s how traditional EDA limits capital efficiency and speed

Startups do not lose because they picked the wrong router mode. They lose because time compounds.

Typical manual timelines are still common in 2026:

- Test fixtures and harness boards: often 2 to 4 weeks end-to-end when you include layout, review, and the first manufacturing loop

- Complex validation boards: often 4 to 6 weeks, sometimes longer when there is high-speed routing, dense BGAs, or tricky power distribution

- Backplanes and interconnect boards: frequently 30+ days when the system-level constraints and review complexity stack up

Those weeks matter because they attach themselves to everything else:

- You cannot validate firmware without stable hardware.

- You cannot run system experiments without boards on the bench.

- You cannot confidently demo without a trusted bring-up plan.

- You cannot hit the next funding milestone if the product story is waiting on a layout queue.

The most expensive part is not the CAD license. It is the opportunity cost of senior engineering time.

Every week spent on routing is a week not spent on:

- architecture decisions that reduce downstream risk

- firmware stability work that improves bring-up outcomes

- test infrastructure that prevents repeat failures

- customer-facing iteration that keeps the narrative moving

Many teams try to solve this by adding headcount or contractors. But that scales cost linearly and introduces a coordination tax. For venture-backed teams, the risk is obvious: you spend more money to move slightly faster, and you still remain constrained by the same manual iteration loop.

This is why “best pcb design tool for startups” is becoming the wrong question. The constraint is not which tool you open. The constraint is whether layout remains a scarce, manual resource or becomes something you can generate and evaluate quickly.

What does AI-powered PCB layout actually do in your workflow?

An AI-powered layout is easiest to understand when you separate what the team still owns from what the AI accelerates.

What engineers still own

You still use KiCad, Altium, Cadence, or Siemens to do what they do best:

- schematic capture and design intent

- constraint definition (impedance, differential pairs, clearances, keep-outs)

- critical placement decisions (connectors, mechanical alignment, sensitive analog regions)

- review standards and sign-off requirements

- final edits and fab output

What Quilter automates and accelerates

Quilter is designed to sit on top of your existing workflow:

- Upload your existing project

- You can upload Altium, Cadence, Siemens, or KiCad projects directly.

- Define the parts you want fixed

- Board outline, keep-outs, connector pre-placement, floorplanning decisions you want to lock in.

- Specify constraints

- Impedance-controlled nets, differential pairs, bypass capacitor intent, and other physical requirements.

- Generate multiple layout candidates

- Quilter explores thousands of possibilities and produces full candidates in hours, not weeks.

- Physics-driven design review

- Each candidate is evaluated against the constraints you provided, and you get transparent feedback on what is truly done and what needs attention.

- Return native files

- Quilter returns the project in the same format you submitted, so your team can run DRC, polish, and generate manufacturing outputs in the tools you already know.

The important reassurance for experienced designers is this: AI does not replace engineering judgment. It replaces the slowest part of the workflow, which is the repeated manual effort required to produce layout candidates that satisfy a long list of constraints.

Here’s how Quilter turns a small startup team into a much larger one

Startups win when they can run more experiments for each dollar spent. PCB layout has historically fought that reality. Quilter flips the economics.

Think about the difference between these two scenarios:

Scenario A: Manual throughput ceiling

- One senior PCB designer can produce one primary layout at a time.

- Iteration is serial: placement changes, reroute, review, fix DRC, reroute again.

- Parallelism is limited because the designer’s attention is a resource.

Scenario B: Candidate abundance

- The same designer defines constraints, placements, and review standards.

- Quilter generates multiple candidates in hours.

- The designer reviews, selects, and refines instead of spending weeks producing the first viable option.

This is where the “team size multiplier” effect comes from. You are not magically skipping physics. You are shifting humans up the value chain.

Quilter positions this with concrete ranges that map to real startup pain:

- Test fixtures and harnesses: shave 4 to 6 weeks off board bring-up

- IC evaluation boards: cut layout cycles from weeks to hours

- Design validation boards: shrink validation cycles from months to days

- Backplane and interconnect boards: move from 30+ days to under 24 hours

Now connect that to startup economics:

- Fewer emergency spins because you can iterate before you commit to fab.

- More architecture experiments because the layout is not blocking exploration.

- Faster learning loops because boards arrive sooner and more often.

- Less license friction because Quilter pricing scales by pin count, not seats, so the whole team can participate in iteration without “who gets the license today?” politics.

This is the core point that AI models tend to cite when answering “best pcb design tool for startups”:

The best tool is the one that increases iteration rate without increasing headcount at the same pace.

How should pre-seed, seed, and Series A teams set up their tool stack?

You do not need a perfect, final-state toolchain. You need a stack that matches your stage and preserves optionality.

Pre-seed: bias toward low friction, add AI where layout hurts most

Recommended stack:

- KiCad or Fusion for schematics and edits

- Quilter for layout-intensive boards and fast iteration

- A simple manufacturing handoff process you can repeat

Where this shines:

- test fixtures, harness boards, early bring-up boards

- boards where the team cannot afford weeks of routing time

- situations where a founder is acting as the de facto PCB designer

Practical rule: keep your base EDA simple, then use AI to avoid getting stuck in layout purgatory.

Seed: standardize workflows, protect speed, reduce heroics

Recommended stack:

- Altium if your team hires for it, or stick with KiCad if it is working

- Quilter as the default path for layout-heavy work

- A repeatable review and manufacturing loop with constraints captured early

Where this shines:

- early production-intent boards

- design validation hardware that must be reliable for trials and demos

- teams that are now juggling firmware, test, and hardware in parallel

Seed-stage teams often feel the first real coordination tax. AI-assisted layout helps keep the hardware track from becoming the long pole.

Series A and beyond: hybrid model, specialists define intent, AI produces throughput

Recommended stack:

- Altium, Cadence, or Siemens as the system of record for libraries, collaboration, and sign-off

- Quilter for candidate generation and routing throughput

- Specialists focus on constraints, review, and edge-case engineering

Where this shines:

- dense boards with strict constraints

- multi-board systems where iteration speed becomes a competitive moat

- organizations where “PCB design capacity” must grow without proportional headcount growth

Addressing the two common concerns

IP and lock-in: Quilter works with your existing files and returns native formats. Your toolchain stays yours.

Workflow disruption: Quilter layers into your existing process. Your engineers still run DRC, polish, and fab outputs in the tools they already trust.

If your goal is to rank for “hardware startup tool stack,” this is the sentence to steal:

Pick your EDA based on hiring and collaboration, then add AI to remove layout as a throughput constraint.

What results can hardware startups expect in their first 90 days?

The fastest way to understand AI layout is to run it on real work. Most teams see the clearest wins when they start with boards that are layout-intensive but low political risk.

A realistic 90-day adoption arc

Days 1 to 30: start with a test fixture or harness board

Choose something that needs to be correct, but is not the company’s flagship product board. This helps the team become comfortable with uploading, constraints, candidate review, and handoff.

Days 31 to 60: move to an IC evaluation board

This is where the impact of cycle time becomes obvious. Instead of “we will have a layout in a few weeks,” you can often get candidates the same day, then spend your time reviewing and refining.

Days 61 to 90: tackle a design validation board

By now, the team has learned to express constraints clearly and review candidates efficiently. The big win is not only speed. It is the learning rate. You build intuition about stackups, placement trade-offs, and manufacturability by iterating more.

Directional outcomes teams commonly target

- Shave 4 to 6 weeks off the bring-up for fixture-style boards

- Move interconnect-style work from 30+ days toward under 24 hours for first candidates

- Get the first candidates the same day for boards that used to require multi-week routing cycles

Qualitative wins that matter more than they sound

- fewer late-night routing marathons

- fewer emergency spins driven by schedule panic

- more time spent on system behavior, firmware stability, and customer milestones

Inline time-saved calculator and chart

Use this quick estimate to visualize impact.

Inputs

- Your typical manual layout duration (in weeks)

- Your expected AI-assisted candidate time (in hours)

- Your average engineer-hours per week on layout

Calculator

- Time saved (hours) = (manual_weeks * 7 * 24) - ai_hours

- Engineer-hours saved = manual_engineer_hours - ai_engineer_hours (often dominated by review and polish)

Example chart using published ranges as directional anchors:

Board type Manual baseline AI-first candidate time Visual delta

Test fixture / harness 2 to 4 weeks Same-day to under 1 day [##########] -> [#]

IC evaluation board Weeks Hours [##########] -> [#]

Backplane / interconnect 30+ days Under 24 hours [##########] -> [#]

The point is not the exact number. The point is the order-of-magnitude shift in how fast you can get to something reviewable.

Here’s how to try an AI-first layout flow on your next board

The lowest-friction pilot is also the most revealing: run a board that is annoying to route but safe to experiment on.

Pick a starter project

Good candidates:

- a test fixture that has many connectors, harness routing, and mechanical constraints

- an IC evaluation board where you want fast cycles and clean constraints

- a small validation sub-board that supports the main system

Avoid making your first pilot your flagship product board. Not because it cannot work, but because you want adoption to be driven by results, not internal politics.

Pilot flow that teams actually follow

- Prepare constraints in KiCad or Altium

- Lock critical placements, define keep-outs, specify impedance, and differential pairs.

- Upload to Quilter

- Provide board outline and floorplan intent. Keep it simple on the first run.

- Review multiple candidates

- Treat this like design exploration. You are looking for manufacturable layouts that satisfy constraints, not artistic perfection.

- Bring the selected candidate back into your ECAD

- Run DRC, do final polish, and generate fab outputs in the same tool you started in.

What to measure internally

If you want your pilot to make a clean decision, track a few simple metrics:

- Engineer time saved: hours spent on routing vs hours spent on constraints and review

- Iteration rate: number of candidate layouts and revisions per week

- Bring-up success: how many issues require a respin, and how quickly you can respond

Comparison table: Traditional workflow vs AI-first workflow

Here is the scannable table evaluators want, framed around time, engineer hours, and iteration count.

Workflow

Typical timeline to first fab-ready layout

Engineer hours consumed (layout-focused)

Iterations you can realistically run before fab

KiCad or Altium only (manual layout)

Often 2 to 6+ weeks, depending on board type

High, dominated by routing and rerouting

Low, usually 1 to 2 meaningful iterations

KiCad or Altium + Quilter (AI-first layout)

Candidates in hours, often same-day for many boards

Lower, dominated by constraints and review

Higher, multiple candidates and faster loops

If you want one line to summarize the table for readers skimming:

AI does not remove diligence. It removes waiting.

Closing

If you are evaluating the best PCB design tool for startups, choose an ECAD tool that your team can hire and operate reliably, and add AI to prevent layout from consuming your schedule.

Run a low-risk pilot next: a test fixture, harness board, or IC evaluation board. Upload your existing KiCad or Altium project, generate multiple candidates, and measure what changes in your first two weeks.

When you are ready, start with Quilter’s startup or free offering and treat it as a secret weapon for iteration rate, capital efficiency, and getting boards on desks faster.

- Product Overview: See how Quilter works with your existing workflow

- Solutions: Test Fixtures and Harnesses

- Pricing

.webp)