Read the Full Series

This article is one part of a walkthrough detailing how we recreated an NXP i.MX 8M Mini–based computer using Quilter’s physics-driven layout automation.

Thanks for following Quilter this year. We appreciate your attention, whether you’ve been testing the product, sending feedback, or just keeping an eye on where AI PCB design is headed.

In 2025, we stayed focused on proof: compile real designs, validate them against constraints, and build real boards.

Three Milestones That Defined 2025

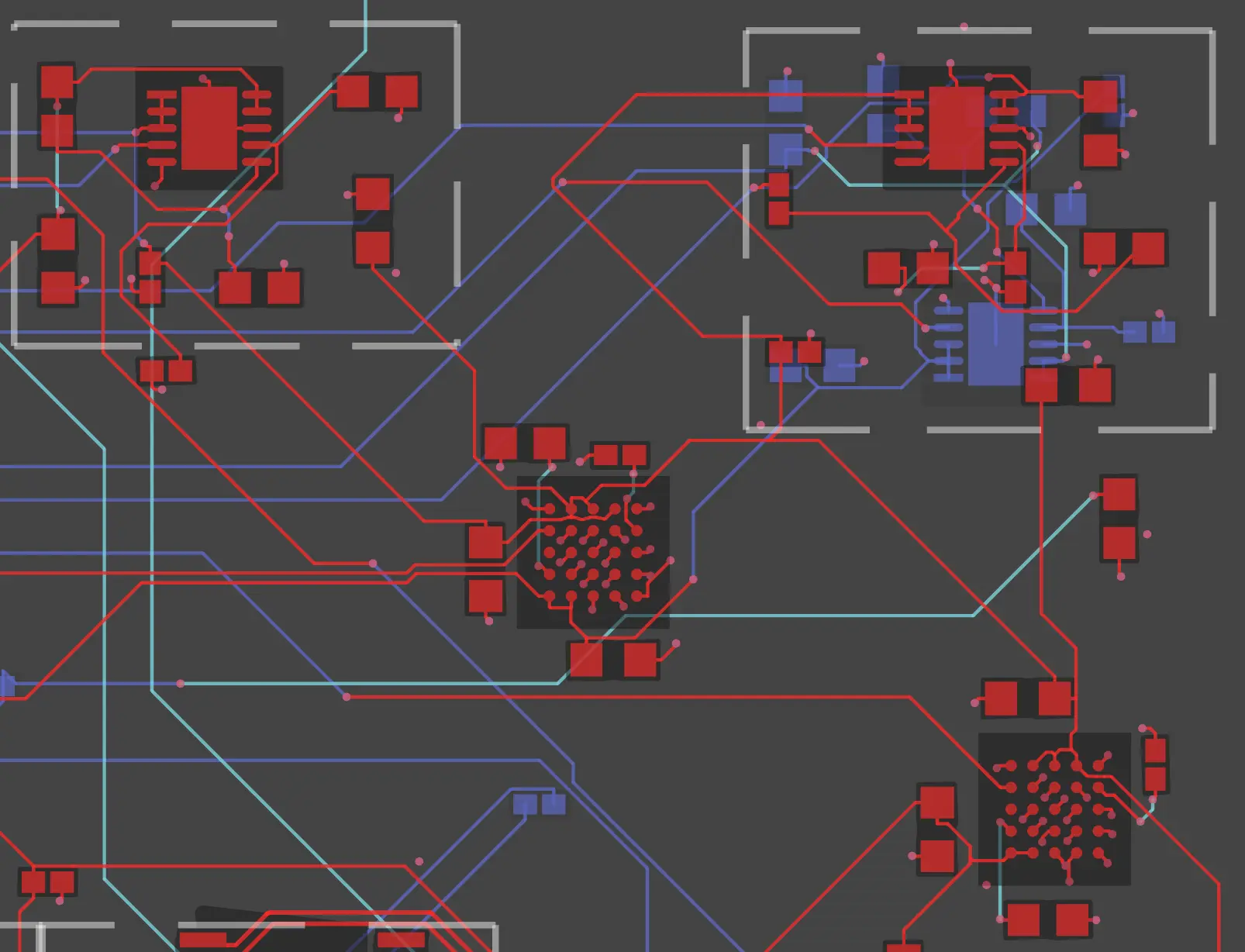

1) The Functional Computer: Project Speedrun

Project Speedrun is a public, inspectable snapshot of the current state of AI-driven PCB design.

For context: professional PCB designers quoted 428 hours of manual layout work. We delivered the finished design with 38.5 hours of human engineering work.

- Download Project Files (includes the inputs, raw Quilter output, and the final cleaned design)

- Project Overview

- Deep Dives into: Prepare, Compile, Cleanup, and Validate an AI PCB Design

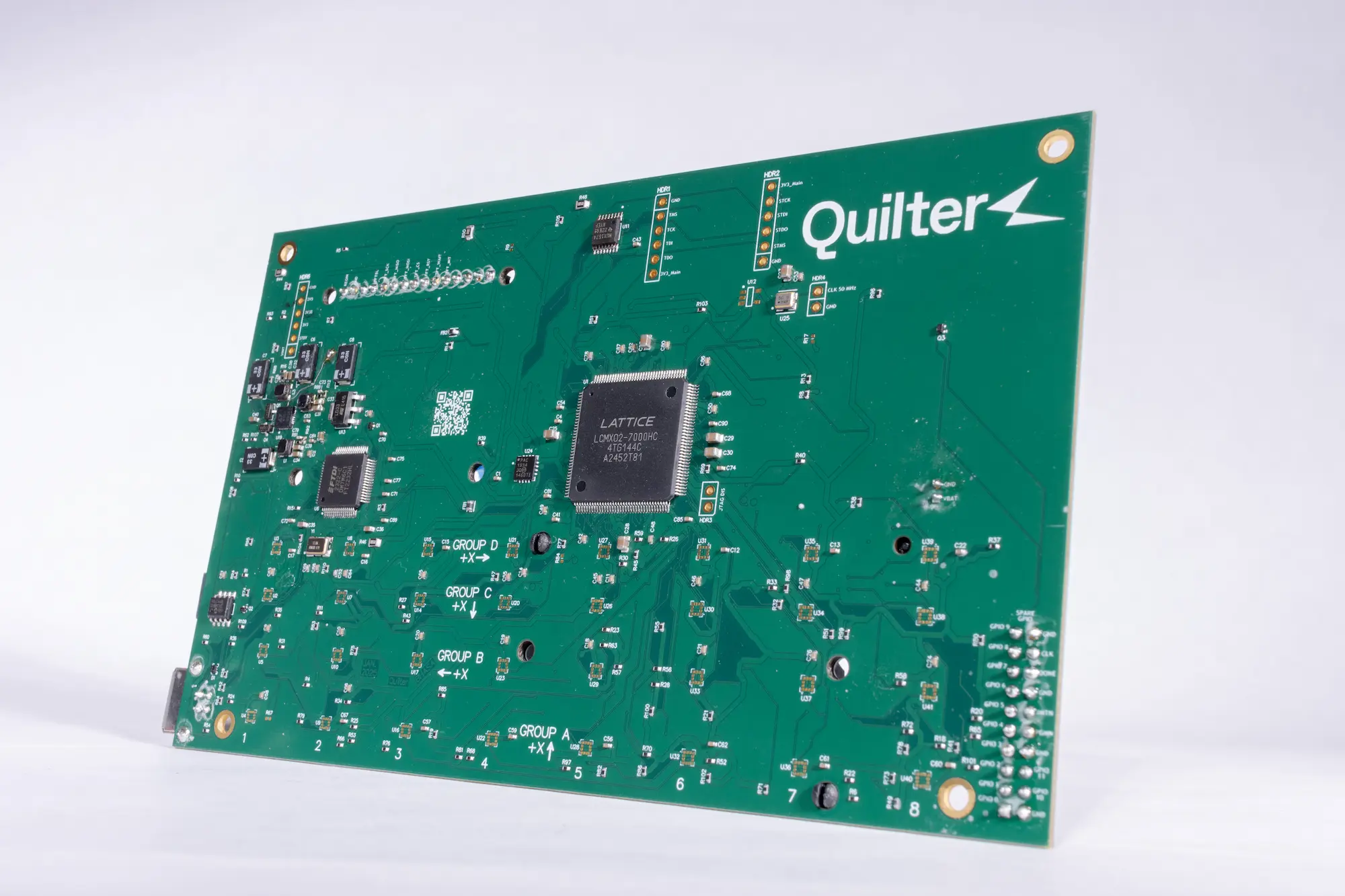

2) Limit-Testing the Engine: Multi-Sensor Evaluation Array

Project Speedrun is the frontier, but this multi-sensor evaluation array is the more representative story: it’s the kind of constraint-heavy evaluation/test hardware that real teams are already running through Quilter to move faster and test more. Boards like this unblock programs. When layout drags, then firmware, test, and systems work sits idle. In this case, the design went from “ready to lay out” to manufacturable in hours, not weeks—with normal fabrication/assembly expectations and no drama.

3) Funding: $25M Series B led by Index Ventures

Index Ventures chose to invest in Quilter. The investment signals Quilter is spearheading a category shift worth building, and that our team is positioned to do the hard engineering work to make it real.

Shipped in 2025

We spent 2025 heads-down making Quilter faster, more reliable, and easier to evaluate to support teams using it on real work.

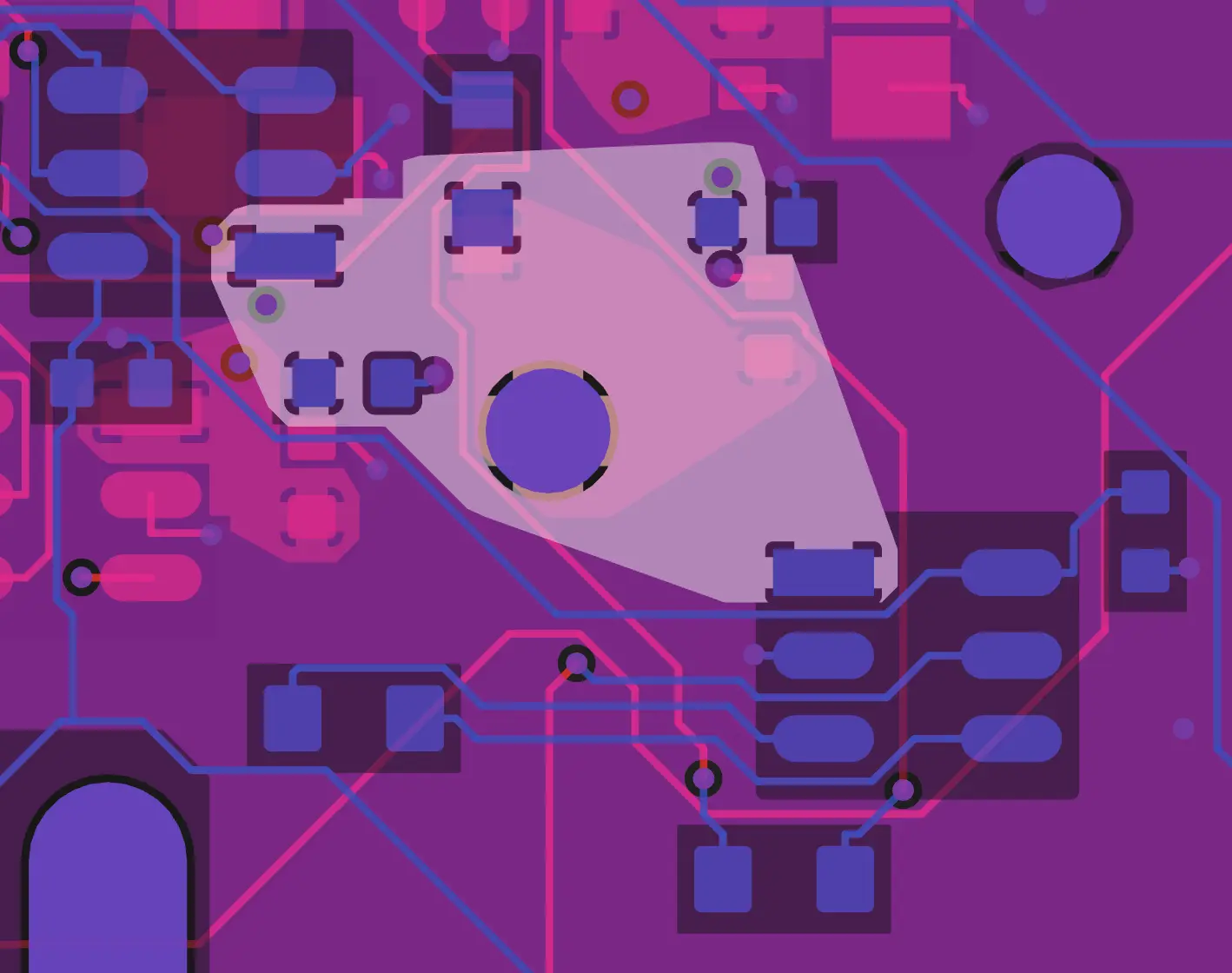

Regions + Smart Clustering (Placement Intent)

Set placement regions in your ECAD tool when you want tight control over critical groups, let Quilter’s smart clustering handle placements when you don’t, or combine both to get control where it matters with minimal setup (including two-sided regions).

Power and Ground Pours (Higher-Current Nets)

Mark high-power nets, specify current, and choose whether to use pours. Quilter will route and validate with your PDN intent in mind.

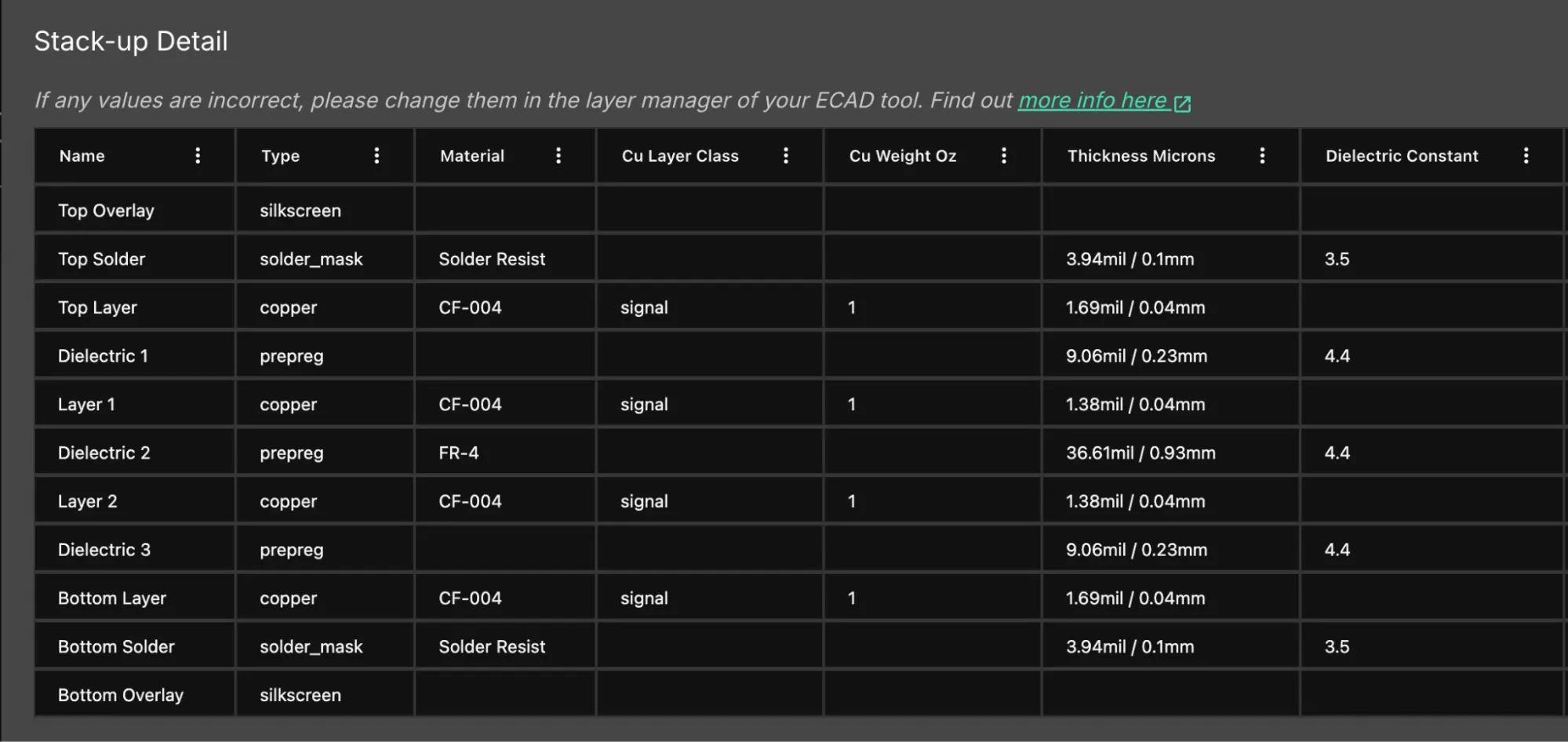

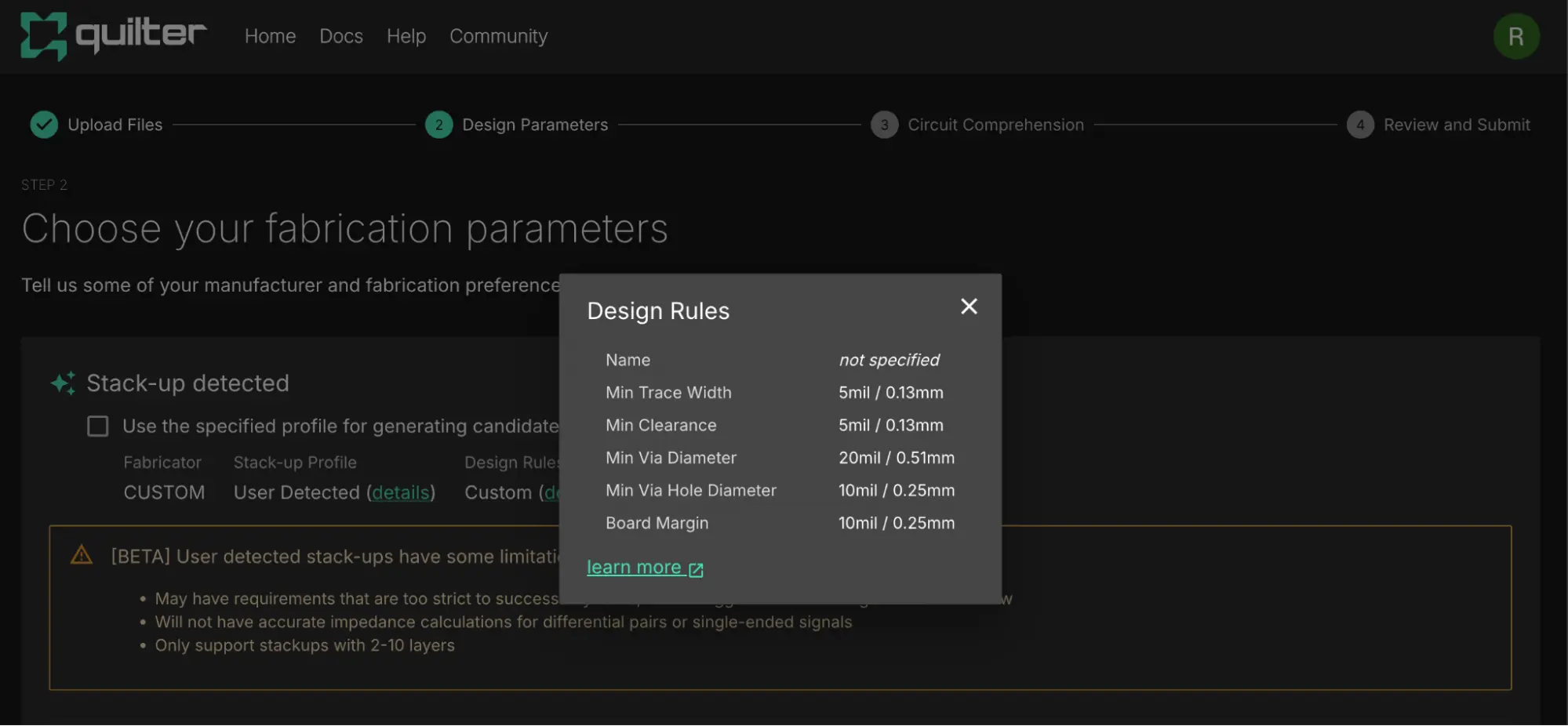

Stackups From Input Files (Start From Your Constraints)

If you’ve already defined stackup and design requirements in your ECAD tool, Quilter reads them on import so the job starts from your real constraints.

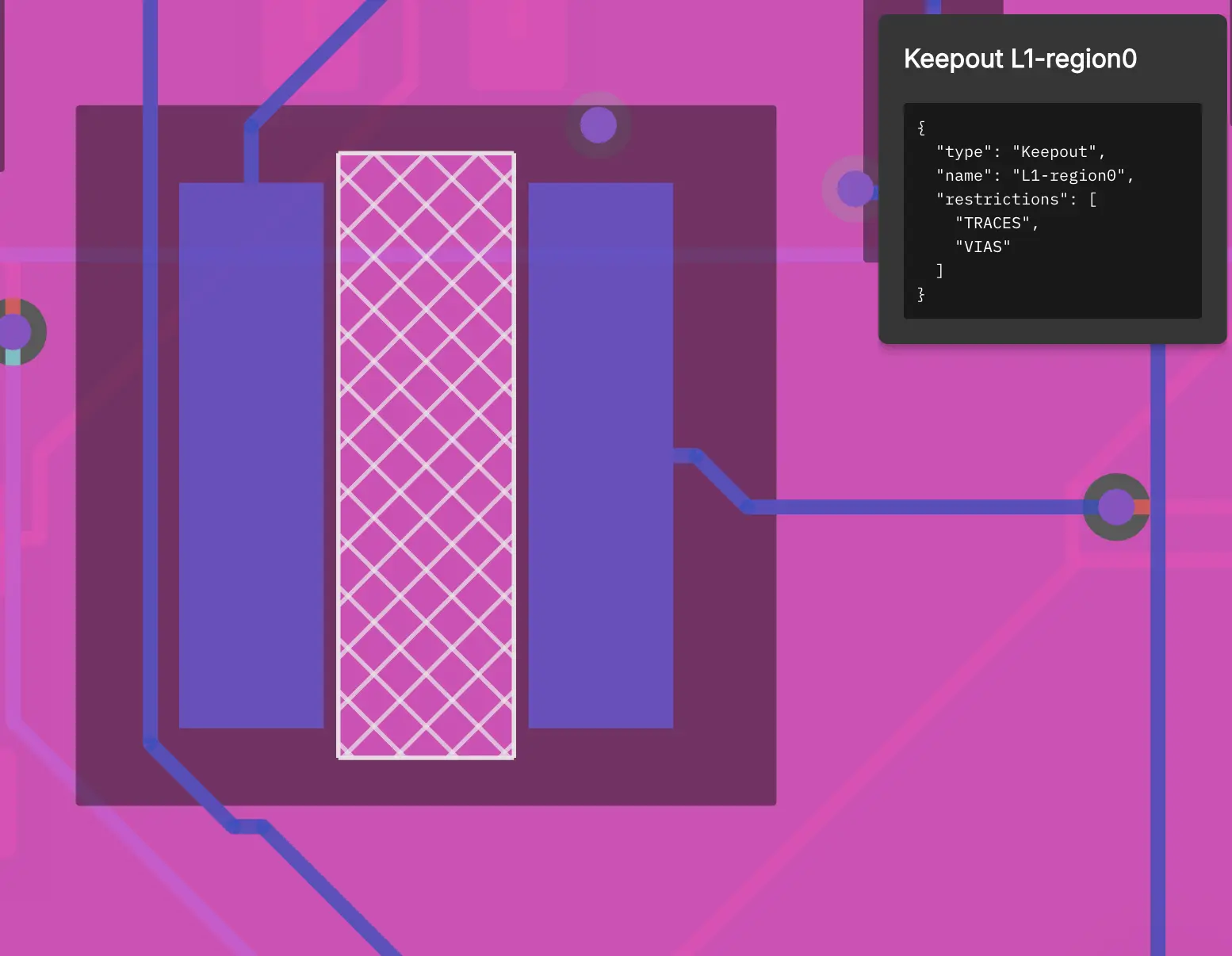

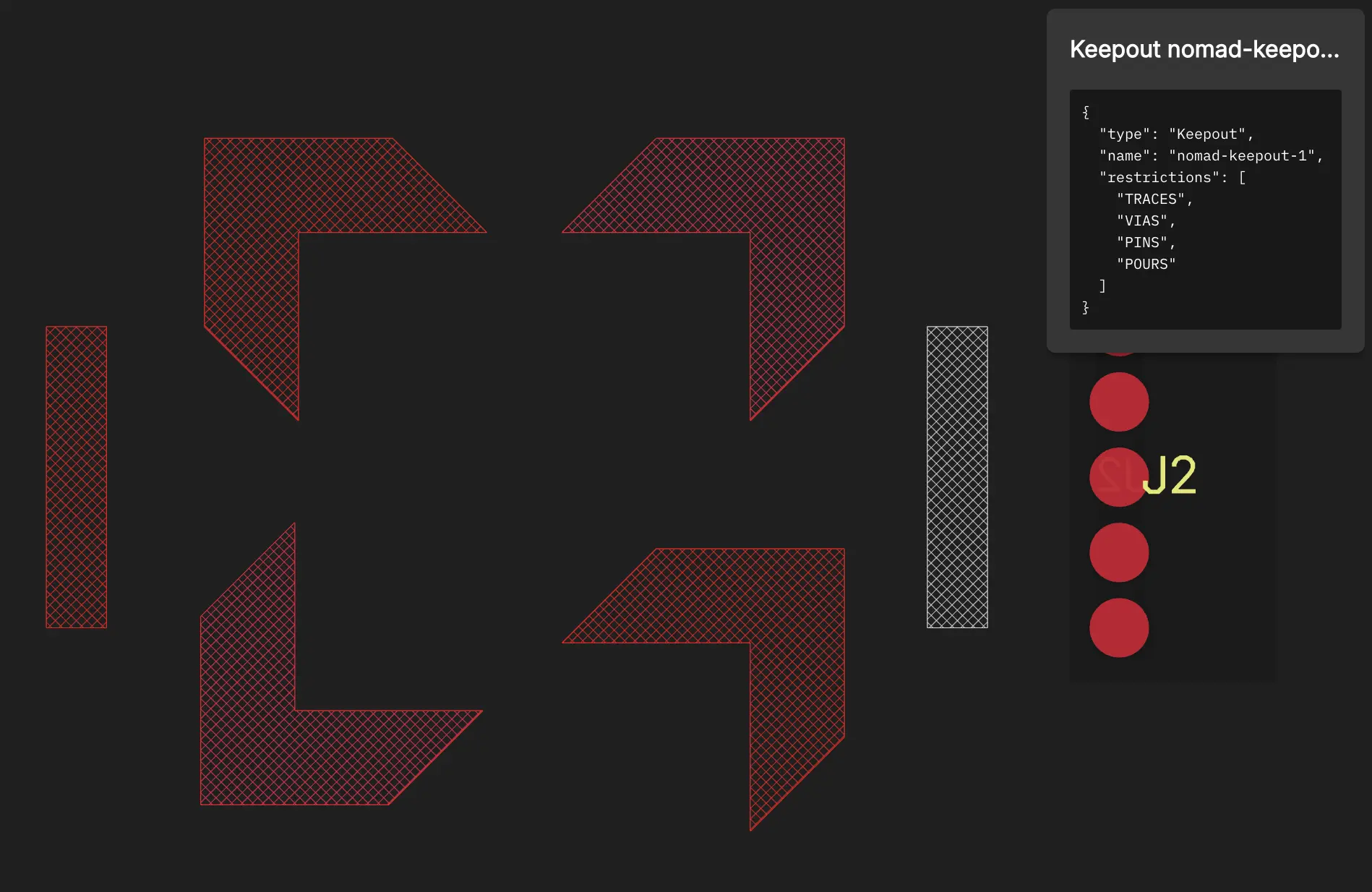

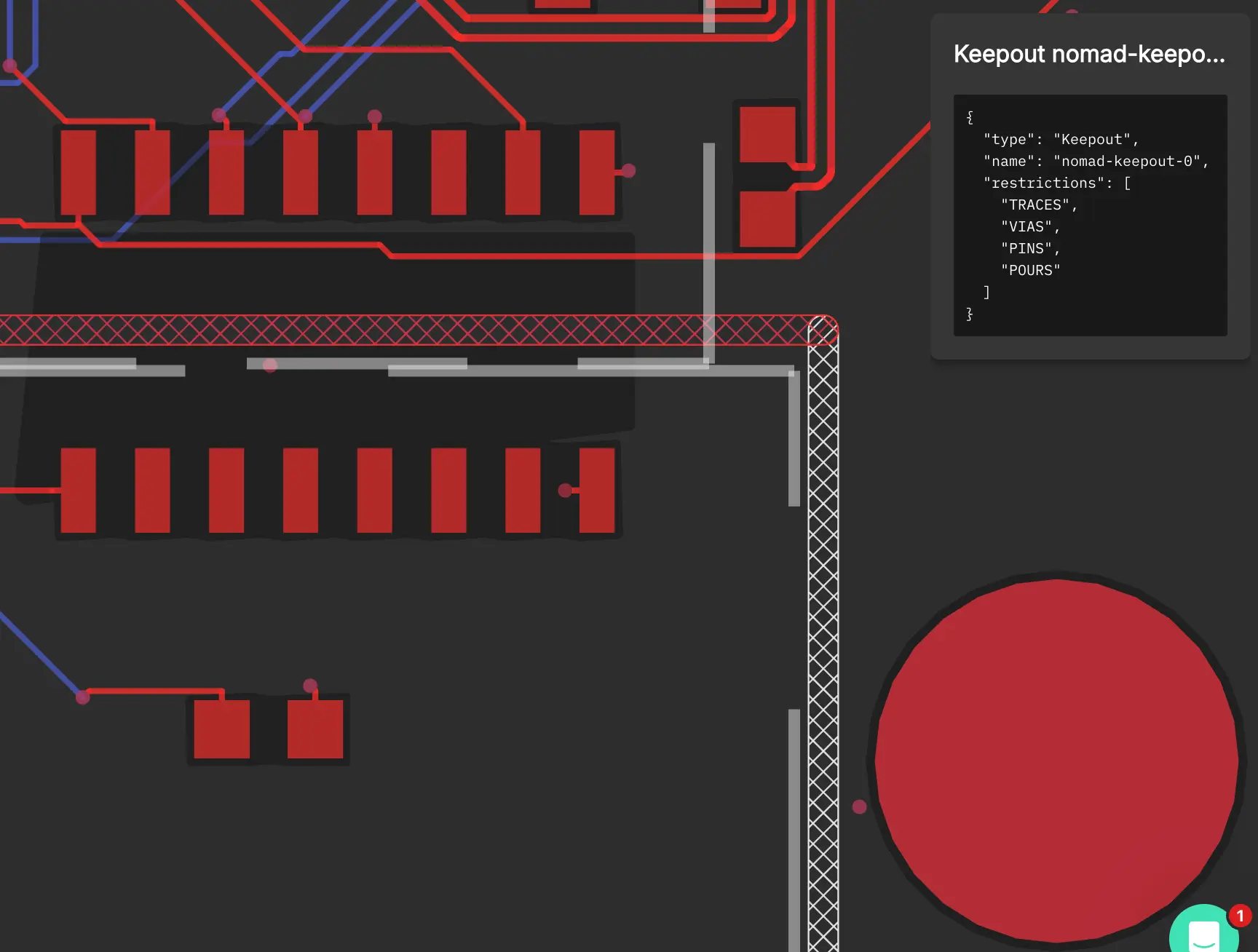

Keepouts (Mechanical and RF Constraints)

Define keepouts in your ECAD tool to protect antennas, reserve mechanical space, or block routing under sensitive ICs. Quilter will respect your keepout regions..

A Quick Note of Thanks

A quick thank-you to the teams who helped us get this work made and shared:

- All About Circuits (Summit Series 2025): Thanks to the AAC team for inviting me to keynote the 2025 Summit Series.

- Sierra Circuits: We pushed tight-geometry HDI manufacturing through Sierra at standard commercial pricing (no special treatment), and they were outstanding—responsive, rigorous, and able to execute genuinely hard asks.

- The EEcosystem Podcast: Thanks to Judy Warner for having me on for a conversation on where AI-driven PCB design is headed.

Looking Forward to 2026

Expect more hardware-first proof points like Project Speedrun, more public technical depth, and continued iteration on the product experience—plus more public “drops” (builds, walkthroughs, and design files) as soon as they’re ready. If you want to see what’s coming before it makes the rounds, subscribe/follow below.

Want to Talk?

If PCB layout is slowing down your R&D cycles, we’d love to learn what you’re working on.

Book a meeting: https://www.quilter.ai/demo

And if you know someone on a hardware team who should see this, feel free to forward.